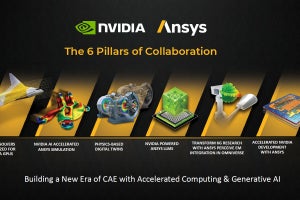

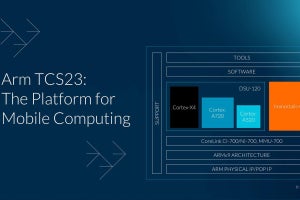

今年のCOMPUTEXに合わせてArmがTCS23を発表した話はすでにレポートしたが、CPU/GPU/Interconnect共にごく概略を示しただけである。実際にはもう少し細かい話が開示されたので、ここでご紹介したいと思う。まずはCPUについてである。

TCS23ではCortex-X4とCortex-A720、Cortex-A520の3つのCPUコアが提供される事になる。この3つはいずれもArmv9.2aベースのプロセッサ(Photo01)であるが、それに加えてもう1つ、32bitのサポート廃止が挙げられる。つまりTCS23ではAArch32のプログラムは実行できない。TCS22のCortex-X3やCortex-A715も実はAArch32のサポートは削られているのだが、Cortex-A510にはAArch32のサポートがあるため、AArch32のプログラムはCortex-A510でのみ実行するという形で対応できたのだが、遂にTCS23ではこれが削られた形だ。

-

Photo01:以前の説明にはQARMA3の話は無かったと思う。これはPAC(Pointer Authentification)用のアルゴリズムで、Armv9.0aで実装されたQARMA5よりもOverheadが少ない(PACを利用する場合のOverheadを1%未満に抑える)というものである

Cortex-X4

さて、まずはハイエンドのCortex-X4であるが、Cortex-X3比で10%のIPC向上を果たしたとする(Photo02)。

-

Photo02:縦軸が記載されていないので推測だが、一目盛あたり3%位のIPC向上率(Cortex-X1が基準でこれが0%)というあたりではないかと思う。とすると、Cortex-X1比では20%近い性能向上率ということになる。ちなみにいずれも同じ動作周波数で、L2のサイズやメモリ帯域なども同等の場合である

さらに言えばL2も最大2MBまで搭載可能である。2MBといえばすでにRaptor Lakeと同等である。SharedのL3と異なり、Core単位でPrivateなL2にここまで突っ込むという辺りが、かなりリッチな構成である。

ただパイプライン構造を考えれば、これも納得である。Front-end、Decodeは10命令/cycle構成の重厚なもの。条件分岐ユニットも強化されたということで、“Perceptronベースの2nd Predictionが入った?”と確認したものの、詳細は説明できないとされてしまった。

-

Photo03:パイプライン段数も、AArch64の命令デコードから数えて10段で、これはCortex-X3より1段少ない。ちなみにCortex-X3ではMicroOpsベースだと若干変わるが、これがCortex-X4では同一になった、というのもやや興味深い

Front-endがこれだけ重厚なのだから、Back-endも当然負けていない。なんと整数段は8ALU/3BUという強烈な構造。FPUも4命令/cycleの処理が可能である(Photo04)。

Schedulerは最大384命令のIn-Flightが可能となっている。当然AGUも強烈で、AGUが4つで、これとは別にStore Dataが直接実行できる仕組みである。AGUがLoad×2、Store×1、Load/Store×1という組み合わせで、2 Load/1 Storeは常に実行可能で、あとは状況次第でLoadかStoreを1個実行できるようにしている訳だ。恐らくSVEを使っている時はStore、AArch64の実行中はLoadとして主に動くものと思われる。

もう一段踏み込んだ細かい話は無かったが、結果としてCortex-X4はCortex-X3と比較してトータルで13%のIPC向上に繋がった、としている。まぁこれだけ重厚な構造になっていたら、それは10%以上向上していても不思議ではない。もちろんアプリケーションによってIPCの向上率にはばらつきがあるのは仕方ないが。

ちなみにこれを達成するにあたり、Cortex-X4のエリアサイズはCortex-X3の10%増し(同一プロセス、L2容量が同じ場合)とされている。ただターゲットプロセスはTSMCのN3Eで、すでにN3Eを利用したテストチップのTape outも済んでいるという話であり、Cortex-X3がN5/N4だったことを考えると、プロセスの微細化で十分吸収できる範囲とも言える。

Cortex-A720

Cortex-X4がこう「力こそパワー」とでも言う感じの、強烈なデコード段と実行段の強化により力ずくでIPCを引き上げた感が強い構成なのに対し、Cortex-A720はもう少しソフィスティケートされた形での性能強化が行われている。Photo07はCortex-A78からCortex-A720までの動作周波数/消費電力の関係をまとめた物で、同一プロセスの構成だと同一消費電力ですこしずつ動作周波数を引き上げているのが判る。

-

Photo07:同時デコード数とか実行ユニットの数とかはCortex-A715と完全に一緒であり、ただしすべてのユニットについて設計の見直しを掛けて性能を向上した(というか、同一消費電力での動作周波数を向上させた)との事

細かい説明は無いが、システムレベルでDRAMのアクセス頻度を大幅に減らした(Photo08)というあたりは、何となくImmortalis-G720に実装されたDVS(Deferred Vertex Shading)に近いものを感じる。

いや実装はまったく異なる(これはDSU-120の効用である)のだが。ただCortex-A78と同じエリアサイズでより高い性能が発揮できる、というあたりが一番のセールスポイントということになるだろう。ちなみにCortex-A715はCortex-X1と同等の性能とArmでは説明しており、なのでCortex-A720はCortex-X2ほどではないにせよ、Cortex-X1を上回る性能を実現できるという訳だ。

内部もそんな訳で余り細かい話は無いが、例えばFront-endではMispredictionのペナルティを減らしたり、2段階の分岐予測を入れたりすることで、「性能を引き上げる」というよりは「性能を落とさない」工夫が施されたとする(Photo09)。

Back-endも同様で、先ほどもあったFDIVやFSQRTのパイプライン化に加え、データ移動の効率化とかAGUの改善、Load-Storeユニットの利用効率向上などが挙げられている(Photo10)。

Memory Subsystem(Photo11)も同じで、L2 AccessのLatency削減やケースによってはL2の帯域を倍増、またPrefetch機能の改良などが挙げられている(Photo11)が、いずれも大きな変更ではなく細かな強化というか改良であり、これらを積み重ねて動作周波数向上というか消費電力低減を実現した格好だ。

-

Photo11:L2の帯域、“memset(0)の場合に最大2倍”というあたりは、Load/Storeユニットの強化というよりはL2に何かしらFast Flashの機能が追加されただけ、という気もしなくはない

Photo12はSPEC CPU 2006のSPEC Intを実施した場合の、テストごとの性能と効率、およびDRAMアクセス率をCortex-A715比で示したものだ。これを見ていると、性能や効率はともかくDRAMのアクセス率はむしろ増えてないか? と思わなくもないのだが、h264refとかomnetppなどはアクセス率がむしろ減っている訳で、その意味では多少変化がある事は間違いない。

-

Photo12:Performance/EfficiencyとDRAM readsではグラフの縦軸が異なっているので、一概には言いにくいのだが、概ねPerformanceとDRAM readsが比例している感じがする

Cortex-A520

Cortex-A520は、Cortex-X4とは逆に「効率性を最優先」した設計となっている(Photo13)。

-

Photo13:この設計方針そのものは、big.LITTLEが世の中に登場して以来不変ともいえる。逆に言うと、これを堅持したままよく毎世代改良できるものである。改良できる余地を見つけるだけでも大変だと思うのだが

こちらも基本設計そのものはCortex-A510と違いが無い(Photo14)。

2コアで1つのCluster(Arm用語ではComplex)を構成するのも同じだし、L1が32~64KB、L2が0~512KBの範囲なのも同じである。差は左にあるように、Arm v9.2aへの対応と冒頭でも書いたQARMA3 PACへの対応、それとAArch32のサポート削減のみである。

ただ内部は結構ドラスティックに変更された。このレベルで見るとCortex-A720同様に細かなUpdateのみに見えるが、3番目の“Removal/scaling down of some performance feature”という言葉は中々に不穏である。実のところIn-OrderのSuperScalar構造そのものは変化が無いのだが、Cortex-A510がALU×3構成だったのに対し、Cortex-A520はALU×2に減っている(Photo16)。

そもそもIn-Order構成だから、ALUを1個減らしても性能は2/3に減る訳では無く(そもそも3つのALUがフルに動くという状況が稀である)、であればALUを1個減らしてエリアサイズや消費電力を減らした方が賢明という訳だ。その分動作周波数を上げたりは細かな改良でALUの効率を上げる事で性能的にもカバーできるという形であろうかと思う。実際SPEC2006_int_rateでのCortex-A510とA520の比較を行ったのがこちら。

最大で22%の省電力化、あるいは8%の性能向上が可能であり、あとはどっちに振るかはSoCの構成次第ということであろう。そのSPEC CPU 2006のBreakdownがこちら(Photo18)。

ALUを2つに減らしても、それは性能にはほとんど影響しておらず、むしろ大きく性能を増しているケースも珍しくない。必ずしもALUの数を増やすだけが能ではない、という実例になっているともいえる。

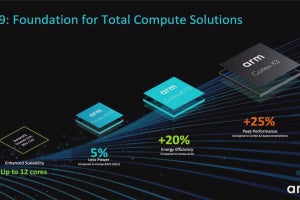

ところでこの3つのCPUコアの使い分け、ということで示されたのがこちら(Photo19)。

TCS22の構成(Cortex-X3+Cortex-A715+Cortex-A510)と、それぞれのコアの役割がオーバーラップする消費電力は大体同じで、ただし性能がそれぞれ伸びる方向になっている。つまり全体としてはTCS22と同じ程度の消費電力で、より性能を引き上げる形で構成される事になると思われる。

DSU-120

このCPUコアを支えるInterconnectとして今回発表されたのがDSU-120である(Photo20)。

TCS22ではDSU-110が利用されていたが、これはTCS21で導入され、TCS22のタイミングで機能強化されていた。ただDSU-120では大幅に性能が向上されており、

- 最大14コアのCPUをハンドリング可能(従来は12コア)

- 最大32MBのL3をサポート(従来は16MB)

- 新たにIntuitive Power Modeを搭載

などが主要な特徴となっている。まずコア数だが、必要なら14コアまでbig.LITTLEのソフトウェアそのままに扱える様になった(Photo21)。

-

Photo21:これは確認したのだが、長らくbig.LITTLE/DynamIQは最大8コアになっていたものの、ソフトウェア的にはTCS22の12コアもTCS23の14コアも問題なく利用できるとの事。それにしても32MB L3ってすでにRyzen並である

ただ特徴的なのはあくまでもCortex向けのInterconnectということで、最小構成ではCortex-A520×4の様な小規模システムにも対応できる事だ(Photo22)。

そうした配慮の1つとして、定常状態における省電力性をさらに向上させたとしている(Photo23)。

内部的には縦横のRing Busを使ったMeshにL3が接続され、さらにその外にCPUへのI/Fが用意されるという形で構成される(Photo24)。

L3は最大8つまでのSliceに分割され、しかもSnoop FilterがそのSliceに付属する形だ。特徴的なのはその省電力機構である。Idleになると、まずL3とSnoop Filterの内容を保持したままSlice Logicをパワーダウンする(Photo25)。

さらに省電力モードになると、L3の内容を半分オフにし、さらに低いレベルでは最後に動作しているコア用のSlice以外すべてをPower Offにするという仕組みだ(Photo26)。

昨今のスマートフォンは、本当に電源をオフにしていない限りは色々処理が常時動いている。通常はそれを一番軽いコア(Cortex-A520)が受け持つ格好であり、それ用のL3までオフにするとむしろメモリアクセスが頻発して却って消費電力が大きくなりかねないから、というあたりがPhoto26右側の構成の目的かと思われる。この結果として、DSU-120とL3の消費電力は最大30%程度まで削減できる、としている(Photo27)。

-

Photo27:Photo26の右側の先が、SliceとLogic、さらにRAMまでパワーダウンする状況である。ただRAMまでパワーダウンさせると、そこからの復帰に時間が掛かるので、通常の状況だとOnly Slice 0 Onの状況程度までの省電力(つまり消費電力60%減)と考えるのが現実的に思う

逆にCortexベースのハイエンド、アプリケーションプロセッサ向けの様なケースでは、最大14個のCortex-X4と32MBのL3という、RyzenやらCore iプロセッサ顔負けの構成が可能になる(Photo28)。

-

Photo28:MPMM(Maximum Power Mitigation Mechanism)は、IntelのAVX Offsetの様な仕組みだ。特にSVEをフルに動かすと消費電力が大幅に増えるので、こうした場合にThrottlingを行う仕組みである

この際の特徴はリニアリティで、14コアをフルに動かした時でも11倍程度まで、直線的に性能がスケールするのが特徴とされる。MPMMは3種類のThrottlingのメカニズムから構成され、Gear 0(一番積極的にThrottlingを行う)からGear 2(一番穏やかにThrottlingを行う)が動的に変更できる。このThrottlingはAMU(Activity Monitoring Unit)という各コアの稼働状況を監視するユニットが実施する。ちなみにArmの説明によれば、MPMMは通常のワークロードでは稼働せず、限界に近い消費電力になるような高負荷の場合にのみ介入するそうだ。またコアからのL3アクセスに関して、Bandwidth PartitioningやCapacity Partitioningの機能も容易されているとする(Photo29)。

-

Photo29:帯域と容量の両方について、コア別に制限が可能で、その制御はMPAM(Memory System Resource Partitioning and Monitoring)が実施する。MPAMはシステム全体で構成されるもので、DSU-120もMPAMを構成する要素の1つではある

ちなみにDSU-120はあくまでCPU間のInterconnectであり、システム自体のInterconnectはCoreLink CI-700やNI-700が担う格好である(Photo30)。

余談だがこの図で「ひょっとしてGPUはACPポートに接続される形態?」と確認したところNoの返事だった。GPU(というか、Mali/Immotaris)はCI-700なりNI-700の先に接続されるとの事だった。

ということで、TCS23の構成要素であるCPUおよびDSUについてご紹介した。次回はGPUをご紹介したい。