ゲートオールアラウンド(GAA)垂直アーキテクチャのメモリセルを備えた3D NANDフラッシュメモリは、高密度データストレージアプリケーション向けにすでに活用されているが、ビット記憶密度をさらに高め、処理コストを抑制するために、GAAの代替としてトレンチセルアーキテクチャが提案されている。本稿は、imecが進めている次世代トレンチベースの3D NANDを実現するための前提条件である3Dトレンチユニットセルの改良されたメモリウィンドウを紹介するものである。

NANDのこれまでの流れ

数十年にわたってNAND型フラッシュメモリは、低コストで大密度なデータストレージアプリケーションの主要なテクノロジーとして発展してきた。この不揮発性メモリは、スマートフォン(スマホ)、サーバー、PC、タブレット、USBドライブなど、すべての主要な電子製品市場で使われている。従来のコンピュータのメモリ階層では、NANDはCPUから最も遠くに配置されており、SRAMやDRAMと比較して、比較的安価で低速かつ高密度であることが知られている。

このストレージテクノロジーの成功は、NAND開発の主な推進力である、密度とコストを継続的に拡張できる能力に関係している。NAND業界では、約2年ごとにビットストレージ密度が向上しており、Gbit/mm2の増加という単位で表される。

この傾向を維持するために、ロードマップ上にいくつかの技術革新が導入された。3次元への移行はおそらく最も印象的なイノベーションだった。3D NANDでは、メモリセルがスタックされて垂直ストリングを形成し、セルは水平ワードラインによってアドレス指定される。その他の注目すべき革新には、セルあたりのビット数の増加(最大4)や、メモリ動作のためのフローティングゲートトランジスタからチャージトラップセルへの移行が含まれる。

300層以上も見えてきた3D NAND技術

すべてのメモリメーカーが追求しているわけではないが、チャージトラップセルは今日のほとんどの3D NAND構造の基礎となっている。このメモリセルは、MOSFETトランジスタに似ているが、トランジスタのゲート酸化物(酸化物-窒化物-酸化物(ONO)スタック)の内側に小さなSiNの層が追加されており、SiN層には静電荷を保持できる電荷トラップサイトが多数含まれている。ポリシリコンゲートが正にバイアスされると、チャネル領域からの電子が酸化物層をトンネルして、SiN層にトラップされる。これにより、トランジスタのしきい値電圧が上昇する。セルの状態は、ソース/ドレインノード間に電圧を流すことによって測定できる。電流が流れる場合、セルは「電子がトラップされていない」状態になる (1に相当)。電流が測定されない場合、セルは「電子が捕捉された」(または0)状態になる。

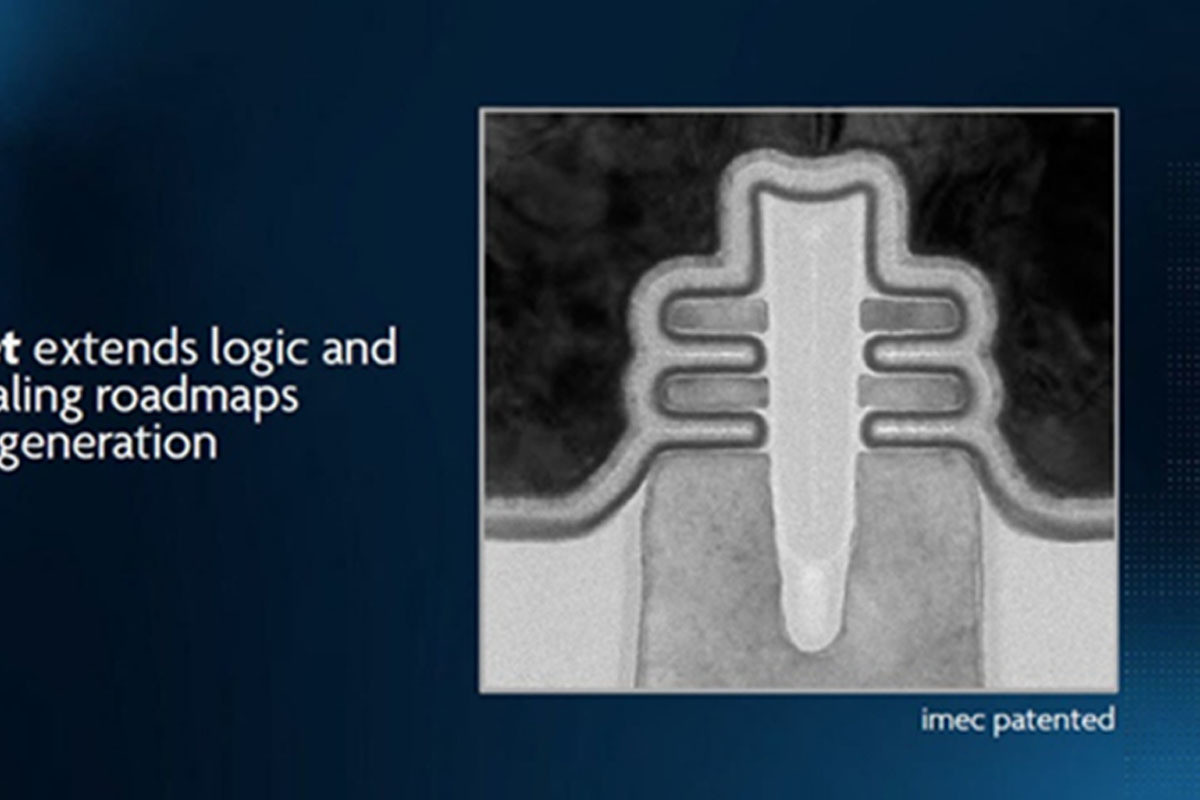

チャージトラップセルは、プログラムと消去の間のしきい値電圧の差として測定されるメモリウィンドウが不十分なため、初期の2D NANDプレーナ構成では導入できなかった。しかし、3D NAND構造では、GAA垂直チャネル実装方式のおかげで、このメモリユニットセルがその潜在力を最大限に発揮できるようになった。このGAA構成では、ゲートスタックがチャネルを完全に包み込んでいる。この円筒形の形状により、トンネル酸化物内に電界効果が生じる。これにより、トラップ層へのキャリア注入が増加し、プログラム/消去ウィンドウが強化される。

GAAの製造は通常、酸化物/ワード線層のスタックを成長させることから始まる。次に、最先端のドライエッチングツールを使用してスタックをドリルダウン(深堀)することにより、円筒形の穴が形成される。次に、トンネル(O)層とトラッピング(SiN)層、およびpoly-Siチャネルがホールの側壁に沿って堆積される。

最近、一部の大手企業は、最大300個のワード線層を積み重ねた3D NAND製品の導入を発表したが、この層増加傾向は今後も続くと予想される。

1000層時代を見据えた技術革新課題

2020年代に、メモリメーカーは従来のGAA NANDファラッシュメモリロードマップを極限まで押し上げることが予想されている。最も楽観的な予測でも、層数は2020年代の終わりまでに1000まで達し、それは100Gbit/mm2ビットの記憶密度に相当することを意味する。ただし、これは、歴史的な密度スケーリングのロードマップと比較すると、数年ほどの減速となっている。

層数が増えると、処理の複雑さとコストがさらに増大し、堆積およびエッチングのプロセスが困難になり、層内に応力が蓄積する。これらの課題を克服するために、業界は最終的に1000層を実現するための、いくつかの補完的なプロセス「トリック」を導入することになる。これらには、層数を2つ(またはそれ以上)に分割すること、セルあたりのビット数をさらに増やすこと、アレイ効率を向上させること、GAAセルのXYピッチを縮小することが含まれている。

また、周辺回路を別のウェハ上で最適化し、ウェハ間ボンディング技術を使用してメモリアレイに取り付ける方向性もある。しかしながら、これらの技術革新は増大する処理コストを制御するには十分ではないため、追加のZピッチスケーリングが追求されている。Zピッチのスケーリングには、ワード線金属や酸化物など、層スタックに含まれるすべての材料の高さの削減が含まれる。

2030年代に期待される3Dトレンチセルアーキテクチャの導入

GAA NANDフラッシュメモリのスケーリングが飽和するであろう2030年に向けてimecでは、チャージトラップセルを接続するための新しいアーキテクチャ、つまりトレンチセルアーキテクチャの導入を予測している。このアーキテクチャにより、3D NANDは円形のGAAメモリセル形状から遠ざかることになる。代わりに、セルはトレンチの側壁に実装されており、平面構成が側面に傾斜するように、トレンチの反対側の壁に2つのトランジスタが配置されることとなる。この次世代NANDフラッシュセルアーキテクチャは、必要なビットストレージ密度の向上を実現するだけではなく、コストも削減できると考えられている。ただし、2D平面構成の場合と同様に、ゲートはチャネルの周りを完全には包み込んでいはいない。したがって、メモリメーカーはプログラム/消去ウィンドウが不十分であることを懸念している。

トレンチセルとGAAメモリセルの動作比較をimecが実施

2023 IEEE International Memory Workshop(2023 IMW)にて、imecはトレンチセルのメモリ動作とGAAメモリセルのメモリ動作の実験的な比較を発表した。両方のNANDフラッシュバリアントは、同じウェハ、つまりpoly-Siゲートと3つのワード線層を備えた独自開発の3D NANDテストビークル上で処理された。円筒形の穴の代わりに、トレンチ構造のワードプレーンスタックにトレンチ構造(幅300nm、長さ1μm)がエッチングされた。3つの垂直平坦poly-Siチャネル(チャネル幅50nm~200nm)がトレンチの側壁に沿って形成され、ソース/ドレイン接合が製造される。

最適化を行わないと、トレンチセルはGAAセルほどのパフォーマンスを発揮しない。これらのプログラム効率と消去効率は理想的ではなく、それぞれインクリメンタル・ステップ・パルス・プログラミング(ISPP)曲線と消去(ISPE)曲線の傾きと開始に反映されている。これにより、プログラム/消去ウィンドウが小さくなる。消去側では、ISPE曲線も消去飽和レベルの低下を示している。

メモリウィンドウが不十分であることは、GAAの場合、トラップ層へのキャリア注入が増加する曲率誘起電界効果が存在しないことで説明できる。この欠点に対処するために、imecではトレンチデバイスのチャネル幅を縮小するという解決策を考え出した。チャネル幅のスケーリングにより、チャネルのエッジの周囲に形成される湾曲した高注入領域の影響が拡大すると予想される。言い換えれば、チャネル幅が減少すると、トレンチセルは幾何学的観点からGAAセルに似てくる一方、消去飽和レベルの劣化は主にゲートからの寄生電子注入によって決まるが、これはゲートスタックを慎重に設計し、メタルゲートを統合することで抑制することができる。

そこでAl2O3の代わりにZrO2やHfO2などの代替のHigh-kライナー材料と組み合わせて、スケールされたチャネル幅(30nmまで)のトレンチデバイスでより良いメモリ動作が達成できることを実験的に示した。人工トンネル酸化物とメタルゲートの統合は、調査した条件のほとんどで、保持およびサイクル動作に影響を与えることなく、5Vというメモリウィンドウが実証された。imecでは現在、プログラムと消去動作のさらなる改善に取り組んでいる。

{#ID6}超高ビットストレージ密度

良好なメモリ特性を備えたトレンチメモリユニットセルが実証されれば、その次のステップは、より多くの層を積層するための潜在的な業界関連の統合スキームを調査することとなる。このようなプロセスフローは、トレンチの側面にある垂直のフラットチャネルストライプをエッチングする追加モジュールを追加したGAAプロセスフローに似ていると予想されている。

この困難なエッチングステップのプロセスソリューションが見つかることを条件として、imecでは220nmピッチのトレンチ(各トレンチの幅が100nm、長さが約1μm)による3Dトレンチプロセスフローのエミュレーションを提案した。高ビット密度を確保するために、このフローは幅25nmのチャネルストライプを80nmピッチでエッチングすることによって完了する。

最終的な設計構造から、トレンチアーキテクチャはGAAリファレンスよりも3倍高いセル密度を持つことが推定されている。これはチャネルピッチのスケーリングによりさらに改善されることが期待されており、それらの結果に基づく3Dトレンチアーキテクチャは、100Gb/mm2をはるかに超えるビット記憶密度を備えた将来の3D NANDフラッシュメモリの画期的な進歩につながる可能性があると考えられる。

|

|

Maarten Rosmeulen

1993年に物理学で、1994年にマイクロエレクトロニクスおよび材料科学分野でそれぞれ理学修士号をベルギーのKUL(ルーベンカトリック大学)で取得。1995年に電子工学の博士号を同大学から取得後、imecに入社し、プロセス集積、半導体デバイス設計、デバイス解析の分野で活躍。2009年にGaN-on-Silicon Light Emitting Diodes(LEDs)開発プロジェクトリーダーに就任しているほか、2014年よりCMOSイメージセンサ開発を担当。2019年にストレージメモリプログラム担当ディレクタに就任し、現在に至る |