東京工業大学(東工大)は7月5日、同大学を中心とした産学研究プラットフォーム「Wafer-on-Wafer(WOW)アライアンス」との共同研究により、チップをウェハ上に接合する「Chip-on-Wafer」(COW)プロセスおよびWOWプロセスによって、CPU/GPUとメモリを3次元実装するハイブリッド3次元実装技術「BBCube 3D」を創出したことを発表した。

同成果は、東工大 科学技術創成研究院 異種機能集積研究ユニットの大場隆之特任教授らの研究チームによるもの。詳細は、6月11日から16日まで京都で開催されたIEEE主催の半導体回路・実装技術に関する国際会議「VLSI Symposium 2023」にて口頭発表された。

AIやハイ・パフォーマンス・コンピューティング(HPC)などでは、CPU/GPUとメモリとの間で大量のデータを伝送することが要求される。データ伝送速度を秒間100億ビットにまで増加させるには、4000本~6000本の配線が必要となるが、従来の2次元的な配置では配線数をこれ以上増やすことが物理的に困難であり、また伝送距離とデータ伝送速度に比例した消費電力の増大も大きな課題となっていた。

このような課題を解決してさらなる高性能化を実現するため、CPU/GPUとメモリとを立体的に積層するハイブリッド3次元実装技術の研究開発が急ピッチで進められている。しかし、従来の3次元積層による半導体パッケージでは、チップの垂直配線(TSV)同士の接続にマイクロバンプが用いられており、TSVの高密度化やデータ伝送消費電力増大の一因となる寄生容量の低減が困難という別の課題が生じていた。

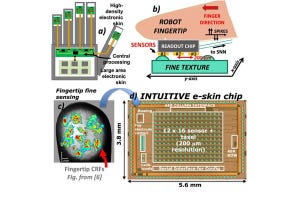

そこで研究チームは今回、銅(Cu)を配線に使用し、埋め込み・研磨によってTSVを行うバンプレスプロセスを用いて、CPU/GPUとメモリとを3次元積層するBBCube 3Dを提案。AI・HPC向け半導体のCPU/GPUとメモリ間のデータ伝送における高帯域と消費電力低減の両立を目指したという。

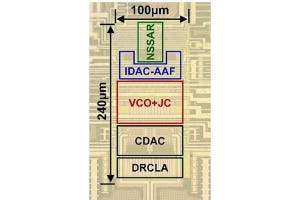

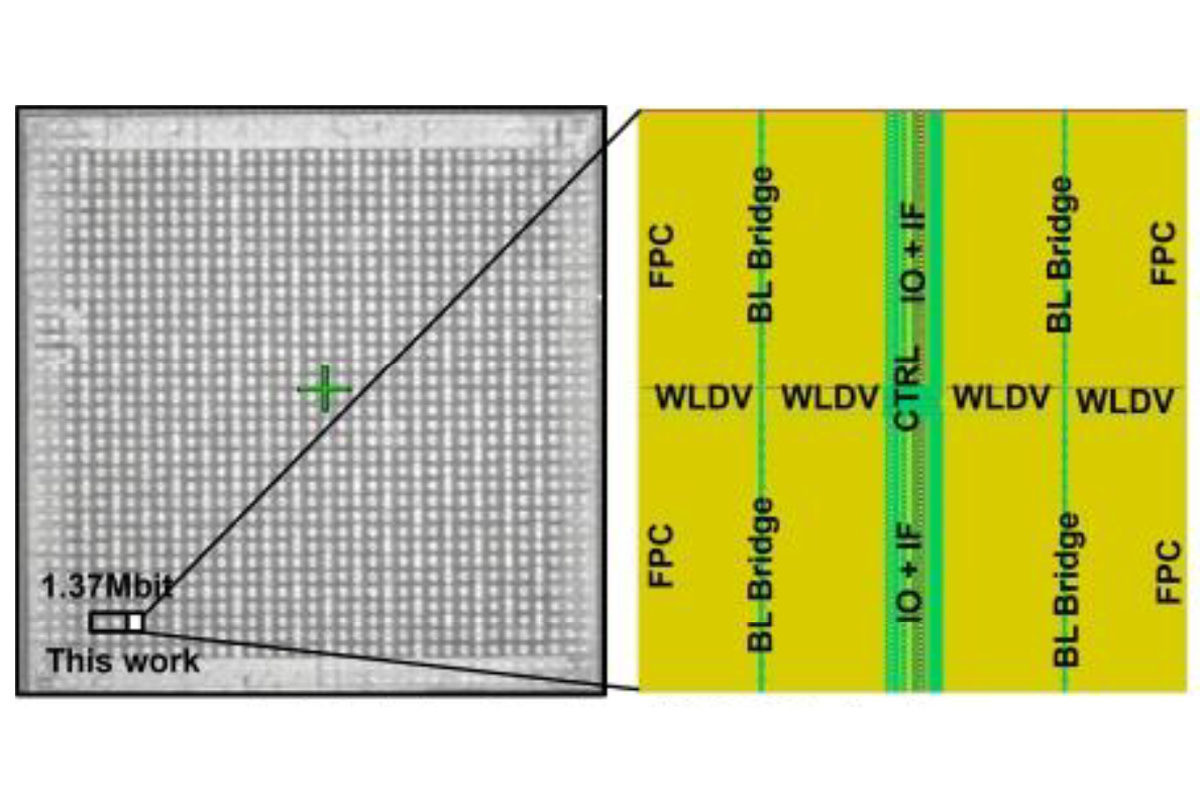

研究チームはまず、ワッフル状にしたウェハ(ワッフルウェハ)にCPUまたはGPUのチップを搭載したのち、モールディングしてウェハを薄化し、TSVを形成。同様に、キャッシュチップをワッフルウェハに搭載してモールディングし、CPU/GPUのウェハに積層して薄化。その後TSVを形成して、CPU/GPUとキャッシュとを接続した。DRAMは、DRAMウェハをキャリアウェハに貼り付けて薄化した後、CPU/GPU、キャッシュを搭載したウェハに積層してTSVを形成し、キャッシュとDRAMを接続。DRAMを必要層数積層した後、ダイシングして個別のチップに分ける手法が取られた。なお、今回のチップとチップのTSV垂直配線にはVia-Last法(Via-Last)が用いられた。

BBCube 3DのTSVの寄生容量を、3次元電磁界解析を用いて計算したところ、従来の3次元実装のTSVに対して16倍の密度を実現しながら、1/20の寄生容量となることが判明したとのこと。この寄生容量は、Si上に2次元的に配置された配線の長さに換算すると、わずか30μm分の寄生容量に過ぎないという(従来なら600μmもある)。

さらにCPU/GPUを垂直に配置すると、CPU/GPU間を接続するTSVは面で配置することができる。チップサイズ(側壁の長さ)で制限されていた従来の実装に対し、BBCube 3Dは、CPU/GPUとメモリを16倍の1万6000本もの信号線で超並列に接続することが可能になるとしている。

CPU/GPUとメモリ間のデータ伝送にかかるエネルギーを解析し、PC/サーバ用メモリ(DDR5)、AIなどに使われる高帯域メモリ(HBM2E)との比較を行ったところ、BBCube 3DはDDR5の13倍、HBM2Eの4倍の高帯域なデータ伝送を実現しながら、電力はそれぞれに対し1/20、1/5に抑えられることがわかったという。

現在、微細化技術の発展は限界を迎えつつあり、DRAMやCPUデバイス単体の競争力は小さくなり、異なるデバイスをまとめたシステムの大量生産が次の競争力となっている。今回の技術は、半導体産業の悩みである微細化の終焉に応えるものであり、次世代半導体システムの道を示すものだとしており、特に性能と生産性の両輪が求められる半導体産業において、300mmウェハプロセスを軸に開発された3次元集積技術は、社会実装に直結し、高い競争力を得ることができるとする。

今回開発されたBBCube 3Dにより、AI・HPC用半導体の電力を大幅に低減することが可能となる。今後は、CPU/GPUとメモリをバンプレスWOW、COWで積層したBBCube 3Dを試作し、大容量データ伝送と低消費電力の両立の実証を目指すとした。