imecは、6月11日から16日にかけて京都で開催されている「2023 VLSI Symposium on Technology and Circuits(VLSIシンポジウム 2023)」において、15件の発表を行う予定で、そのうち13件がimecの研究者が筆頭著者(うち招待講演1件を含む)となることを発表した。

VLSIシンポジウム委員会の集計によると、デバイス・プロセス技術部門で発表される89件のうち、一般講演の最多発表機関はimecの11件だという。発表件数のトップ10は以下の通りとなっている。

- imec(ベルギー):11件

- 国立シンガポール大学(シンガポール):10件

- Samsung Electronics(韓国):8件

- 国立台湾大学(台湾):5件

- TSMC(台湾):5件

- KAIST(韓国):4件

- POSTECH(韓国):3件

- SK hynix(韓国):3件

- パデュー大学(米国):3件

- 国立交通大学(台湾):3件

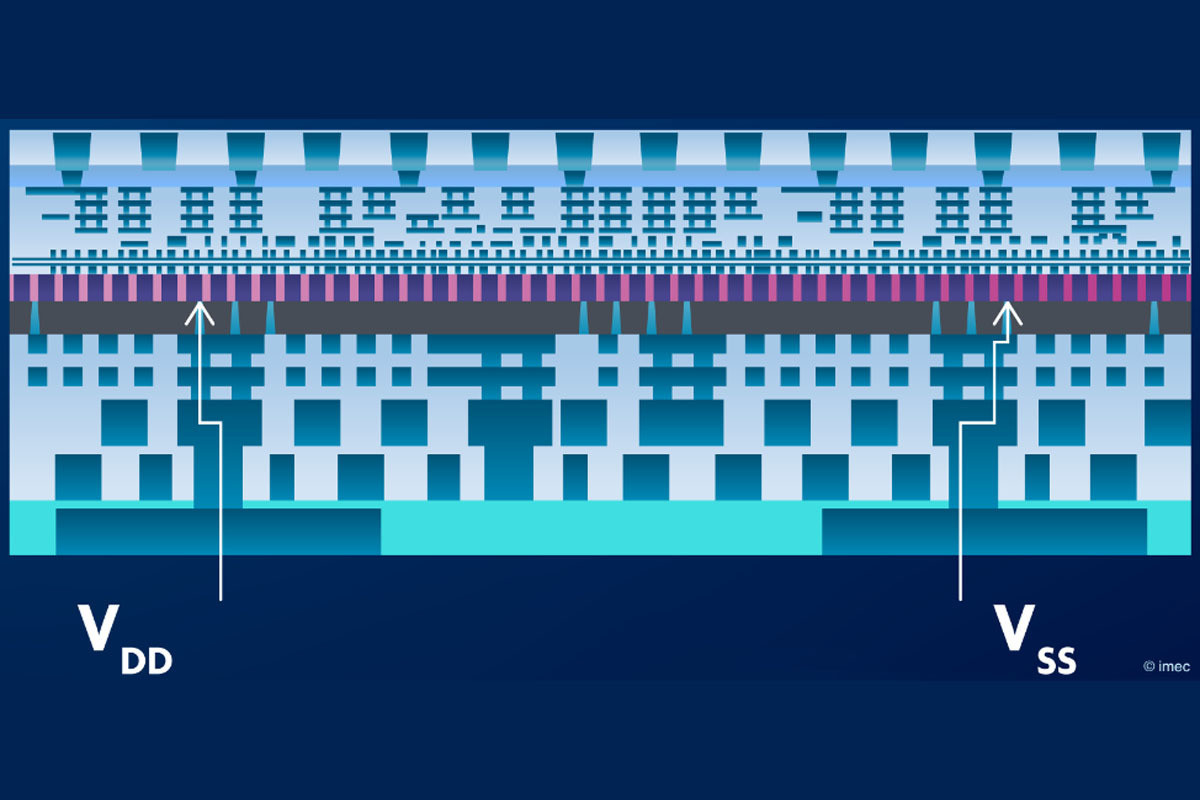

imecでは、バックサイド電力供給ネットワーク(BSPDN)を注目トピックとして挙げており、同シンポジウムでも将来の研究の方向性についての見通しを提供することを目的として発表を行うという。

またGoogle、Intel、ASML、Arm、Cadence、Synopsys、ジョージア工科大学の著名な講演者とともに最先端BSPDNに関するワークショップも開催。このワークショップは、BSPDNの未解決課題を検討し、機能的なバックサイドに向けた将来の研究の方向性についての見通しを提供することが目的だという。

imecではBSPDNに関する研究として4件の論文発表を行う予定で、imecフェローのEric Beyne氏がBSPDN用ナノスルーシリコンビア(nTSV)などによる集積フローと課題を紹介するほか、Armとの共同論文としてN2およびA14ノードでの64ビットプロセッサブロックの埋め込みに対する裏面電源供給の影響の評価結果を報告する予定。これについては、デモセッションでの実演も行われるという。

また、埋め込みパワーレール(BPR)を介したBSPDN配線を使用したDTCOにおけるESD信頼性の今後の課題について報告するほか、電力パフォーマンス領域(PPA)のトレードオフと、3種類の裏面電源接続の評価結果も報告される予定だという。

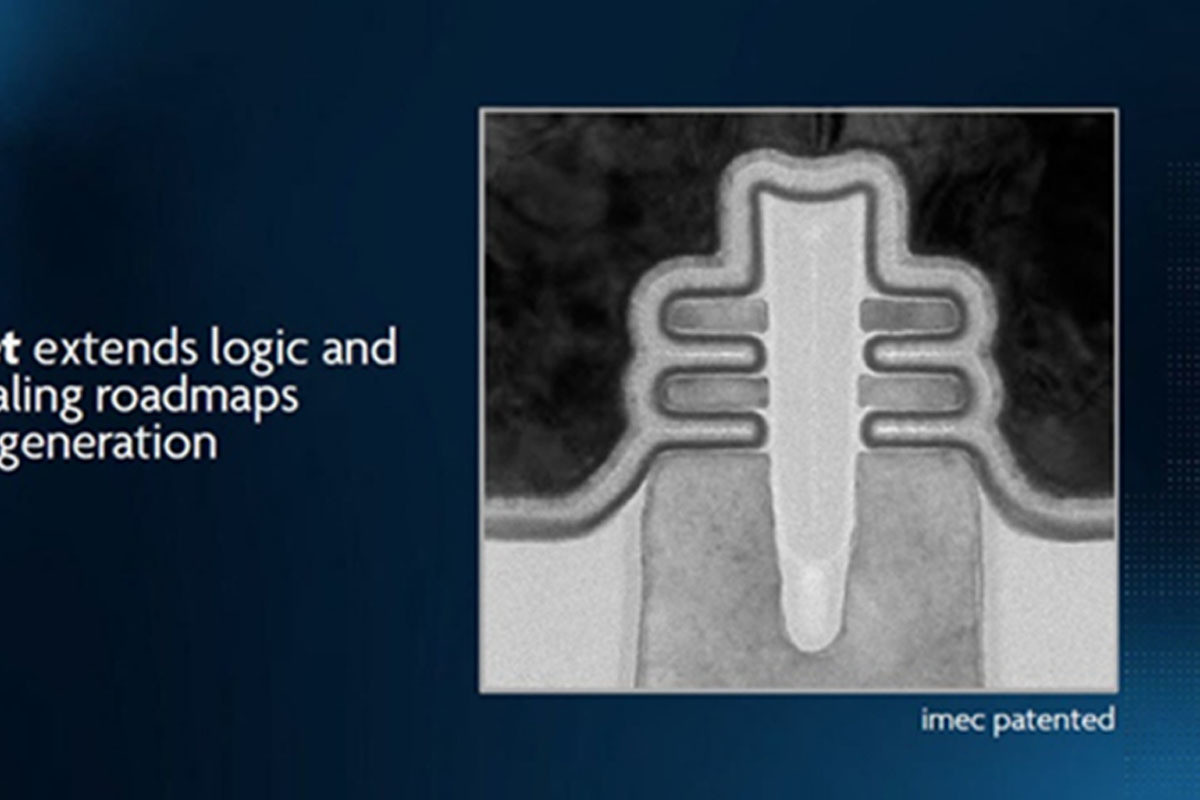

BSPDN以外の分野では、究極のトランジスタ構造と言われるCFETに関する発表が3件予定されている。

- 48nmゲートピッチのナノシートベースのCFET、およびCFETの内部スペーサー形成とマルチVtパターニングを可能にする中間誘電体分離

- CFET用のスケーラブルで熱的に安定したpWFMとしての窒化モリブデン

- モノリシックCFETのためのスタック型コンタクトMOLの統合

これらのほか、以下のような発表も予定されている。

- モジュール統合によるシリコンスピン量子ビットのための包括的な300mmプロセス(講演のほか、デモセッションの実演も予定)

- 一括ダイツーウェハ(CoD2W)転写による300mmウェハ上のエピタキシャル単層MX2チャネルの集積

- 同期パルス原子層エッチングと湿式化学エッチングを組み合わせたアプローチを使用した、MX2トランジスタの低損傷および製造互換性トップコンタクト

- 新しい低熱バジェットCMOS RMG:従来の高熱バジェットゲートスタックソリューションに対するパフォーマンスと信頼性のベンチマーク

- IGZO-TFTの反応性イオンエッチングによりキャパシタレスDRAMの最低IOFF<3×10-21A/μmを達成