東京大学(東大)と奈良先端科学技術大学院大学(NAIST)の両者は6月9日、原子層堆積法を用いて酸化物半導体のナノ薄膜を成膜する技術により、低温で形成可能なナノシート酸化物半導体をチャネル材料とする高性能で高信頼性なトランジスタの開発に成功したことを共同で発表した。

同成果は、東大大学院 工学系研究科の日掛凱斗大学院生、東大 生産技術研究所(東大 生研)の小林正治准教授、NAIST 物質創成科学領域の浦岡行治教授らの共同研究チームによるもの。詳細は、2023年6月11日から16日まで開催の「2023 Symposium on VLSI Technology and Circuits」にて6月15日に発表される予定だ。

現在、半導体の新たな大規模集積化に向けて、3次元集積化によるさらなる高集積化と高機能化が進められている。その一例として、従来のシリコン基板上に形成される半導体集積回路の配線層にトランジスタを形成することで、高機能回路を3次元積層して高集積化することが可能だ。

その実現のためには、低温で形成できる半導体材料が必要であると同時に、その材料を用いたトランジスタが、高集積化のために微細化しても高性能・高信頼性を有する必要があるとする。酸化物半導体は、これまでフラットパネルディスプレイで用いられてきた半導体材料だが、半導体集積回路への応用にはナノ薄膜の均一な成膜が必要であり、それに加え、それを用いた高性能・高信頼性なトランジスタ技術の開発が望まれていた。

そこで研究チームは今回、原子層ごとに成膜が可能で、均一な膜厚が得られる、原子層堆積法による酸化物半導体のナノ薄膜の成膜方法を独自に開発。それを応用し、ナノシート酸化物半導体をチャネル材料とする、高性能で高信頼性なトランジスタを開発したという。

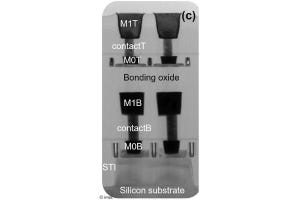

具体的には、酸化インジウム「In2O3」と、酸化ガリウム「Ga2O3」を原子層ごとに交互に成膜することで「InGaO」(IGO)のナノ薄膜を成膜する手法が開発された。そして、ナノシートIGOをチャネル材料とするプレーナー型トランジスタを試作・評価し、性能指標である移動度と信頼性指標であるバイアスストレス閾値電圧シフトを系統的に調査し、移動度と閾値シフトの間のトレードオフ関係が明らかにされたとする。

また、そのトレードオフを解消するために、IGOナノシートをゲートで覆った「Gate-All-Around構造」を提案し、試作評価が実施された。その結果、ノーマリーオフ動作、プレーナー型に対して2.6倍の駆動電流向上、1.2倍の移動度向上、閾値電圧シフトの大幅な低減を実現したとしている。

-

ナノシート酸化物半導体トランジスタの電気特性シミュレーション結果(左上)、実測結果(左下)、移動度(対プレーナー型トランジスタ)(右上)、バイアスストレス閾値電圧シフト(対プレーナー型トランジスタ)(右下)。(出所:東大 生研Webサイト)

今回の研究により、原子層堆積法による酸化物半導体のナノ薄膜の均一な成膜技術が実現された。研究チームは今後、高移動度で高信頼性な酸化物半導体ナノ薄膜の開発を推進し、微細なトランジスタや3次元構造のトランジスタへと展開することで、半導体の3次元高集積化に資する研究開発を行っていくという。研究チームは今回の技術により、半導体のさらなる高集積化とそれによる高機能化が可能となり、エネルギー効率の高いコンピューティングを実現することによって、ビッグデータを利活用する社会サービスの展開が期待されるとしている。