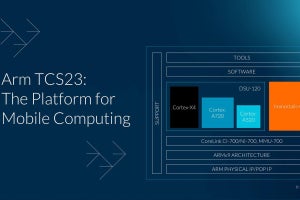

既報の通り、英ArmはCOMPUTEX TAIPEI 2023に合わせて「TCS 23」と、これを構成するCortex-X4/Cortex-A720/Cortex-A520やDSU-120、Immotalis-G720/Mali-G720/Mali-G620を発表した。

発表はCOMPUTEX TAIPEI 2023の開催前日にあたる5月29日で、午前にこのTCS 23の発表会、午後にRene Haas CEO(Photo01)による基調講演という恰好であったが、実は発表会では新情報がまったくと言ってよいほど無かった。ということでまずは基調講演の内容を簡単にご紹介したい。

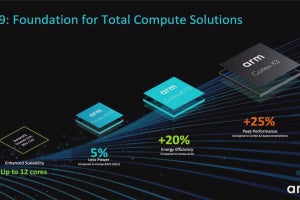

ArmのIPコアはここにきて急速に普及というか出荷数を増やしており、その意味ではDominantなアーキテクチャの座を掴んだことに疑問の余地はない(Photo02)が、その一方で引き続きより高いプロセッサ性能を求めるDemandそのものも変わらず存在している。

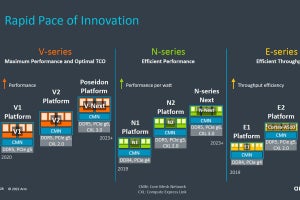

したがって、より高性能なコアを開発し、それをより微細化したプロセスで製造したい、という流れになる。これを妨げる要因は、設計コストの高騰である。7nm世代での設計コストはラフに言って2.5億ドル程度。これが2nm世代になると7億ドルを超える、とされる(Photo03)。

単にコストだけが増えるのみならず、設計のサイクルタイムもどんどん伸びており、こうした問題を解決してゆかないと、前出のプロセッサ性能のDemandに対応できないことになる(Photo04)。

これを解決できるのがAI技術「だけ」なのかどうか断言はしにくいが、確かに直近で見ているとAIを利用したP & R(Place & Route)の効率化とかスマート化以外に有望な技術がないのも事実である。

こうした問題に対する解がArmのIPであり、単にProcessor IPのみならずInterconnectや周辺回路まで含めた包括的なソリューションを利用することで開発期間の短縮化を可能にする、としている。実際Kick-off(設計開始)からTape-outまでを13か月で行った例もあり、これは(ArmのIPを使わなかったケースと比較して)80人年のコスト削減に相当する、としている。

その1つの例が、今回NVIDIAが大々的にアナウンスした「Grace Hopperカード」に搭載されたGrace CPUである。72コアのNeoverse V2で構成されるGraceは、既存のArmベースの製品と比較して10倍のAI性能をより少ない消費電力で達成できるとした(Photo05)。

基調講演としての説明はこの程度であり、強いて行間を読むとすれば「高性能プロセッサの領域ではまだRISC-VはArmの敵ではないし、ソフトウェアのサポートも実績も乏しい」と言外に言っている気はするし、それそのものは事実であろうが、Photo01で出てきた「直近2年で増えた500億個のArm CPU」の大半はこうしたハイエンドプロセッサではなく、むしろCortex-MとかCortex-R、あるいはローエンドのCortex-Aであることを考えると、決してArmの地位が安泰だと安心している訳でもなさそうだ。

32bitアプリのサポートがなくなったTCS 23

さて基調講演ではこの程度であるが、基調講演の翌日にAndy Graigen氏とStefan Rosinger氏(Photo06)にもう少し細かい話を聞くことができた。実はCortex-X4/A720/A520とかImmotalis-G720/Mali-G720/Mali-G620の内部構造の詳細の情報も入手しており、例えばCortex-X4は10命令同時デコードでALU×8+BRU×3+AGU×4という化け物であることなども判っている。このあたりの詳細、つまり本当の意味でのDeep Diveは後程お届けする予定であるが、まずはGraigen氏とRosinger氏にお聞きした話をもとに、Deep Diveのさわりだけをお届けしたい。

-

Photo06:左がAndy Graigen氏(Director, Product Management, Client)、右がStefan Rosinger氏(Senior Director, CPU Product Management, Client Line of Business)

まずCPU側であるが32bitサポートについて。もともとArm v9で32bitをサポートしていたのはCortex-X2とCortex-A710/A510までであり、TCS 22で登場したCortex-X3とCortex-A715では32bitサポートが落ちている。それでもCortex-A510を組み合わせて、32bit Taskを全部Cortex-A510が処理する形にすることでTCS 22では32bitアプリケーションが動作する余地があったが、TCS 23ではすべてのコアが32bitサポートを落としたことで、もう32bitアプリケーションは利用できなくなった。

もっともOSそのものもすでに64bitに移行しており、ほとんどのアプリケーションが64bitに移行した昨今では、少なくともMobile向けに関して言えばそれが大きな問題になる可能性はないと判断したとのことで、これは納得できる。問題は組み込み向けであるが、少なくともCortex-A520が組み込み向けに提供される様になるまでにはまだ時間がかかるし、その間に64bit移行がさらに進むという見通しなようだ。

次にCortex-X4。先に書いたように10命令/cycleのDecodeとか11命令発行のIssue(FPUは別)、AGU×4という化け物な内部構造であるが、これだけ大規模なユニットを1 Threadでどこまで利用しきれるのか? という疑問は当然浮かぶ。「なぜSMTを使わなくても効率を高く保てるのか?」という質問の答えは、一口で言えば「頑張った」であまり細かい話はなかったのだが、分岐予測ユニットを強化したことも貢献しているという話であった。ちなみにその分岐予測ユニットが2段構成になっているのは公開されているが、「PerceptronなどのAIベースか?」と突っ込んだものの「詳細は未公開」と逃げられてしまった。

一方のGPU、基本的にすべてを見直して効率を向上させたことで、2%ほどのエリアペナルティで大幅に性能向上を可能にしたとのこと。こちらの内部構造については、後程詳細を説明予定である。

またImmotalis-G720/Mali-G720/Mali-G620の違いはコア数で、

- Immotalis-G720:11~16core

- Mali-G720:6~10core

- Mali-G620:1~5core

とコア数に応じて製品名が変わるという話であった。

またImmotalis-G720などにはTensor演算ユニットは含まれていないが、これは今後も搭載する予定はないとのこと。「ということは、Super SamplingはNVIDIAやIntelの様なAIベースではなくAMDやImaginationの様なアルゴリズムベースになるのか?」と突っ込んだところ、「そもそもSuper Samplingの機能をまだ提供していないのでその質問には答えられない」と逃げられてしまった。

ということで、Deep Diveのさわりをお届けした。本番のDeep Diveはもう少々お待ちいただきたい。