横浜国立大学(横浜国大)は5月30日、チップレット技術における配線の高密度化を可能にする直接接合技術を用いた、新規チップ仮接合および剥離技術の開発に成功したことを発表した。

同成果は同大 工学研究院(ヘテロ集積研究拠点長)の井上史大 准教授、ディスコ、東レエンジニアリングらの研究チームによるもの。詳細は、5月30日~6月2日にかけて米フロリダで開催される半導体パッケージング技術に関する国際会議「IEEE 73rd Electronic Components and Technology Conference(ECTC2023)」にて発表される予定だという。

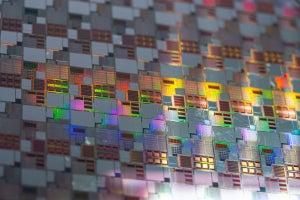

物理的な限界が見えてきた半導体のプロセス微細化に代わって、さらなる高性能化を実現する技術としてチップレットの活用が期待されているが、チップをウェハ上に接合し、垂直方向の電気的な接合を担保する接合/配線技術に関して課題が残されており、その解決法が求められているとする。

今回研究チームではその課題解決に向け、新たに開発されたCVD絶縁膜を用いて、チップをウェハ上にプラズマ活性化ダイレクトボンディングによって仮接合する方法を考案。この仮接合のポイントは、低温で堆積されたSiO2膜による意図的なボイドの形成と制御された接合エネルギーにあることから、表面粗さ、膜組成、機械的特性、プラズマ活性化の影響などの調査を行ったほか、メカニズムの解明に向けた各種の界面解析を行うことで、実現したとする。また、熱脱着分光法(TDS)ならびに陽電子消滅分光法(PAS)を用いた解析から、低温で堆積されたSiO2には多くのオープンスペースと水が内部に含まれており、水の貯蔵層として機能し、ポストボンドアニール中に放出される可能性があることが確認され、これによって熱剥離が可能となり、低い力で簡単にウェハとチップが剥離可能であることも示されたという。

同技術による仮接合界面はほとんどの前工程プロセスと互換性があるため、拡張性が見込めると研究チームでは説明するほか、界面層が薄く固体であるため、ボンディング中のダイのずれのリスクを軽減することができることからDie-to-Wafer(D2W)の「ハイブリッド接合」が可能であり、仮接合による材料の加工時間、材料損失を削減、低コスト化が実現可能になるとしている。

なお、今回開発された技術は、すでに300mmウェハ上に実際に適用するデモンストレーションも実施済みとのことで、研究チームでは同技術により、歩留まり向上、高いボンディング位置合わせ精度、およびコスト削減を伴う高度な異種3D集積が可能となるとしている。