大阪大学 量子情報・量子生命研究センターと富士通は3月23日、量子エラー訂正に必要な物理量子ビット数を大幅に低減し、量子コンピュータの実用化を早められると期待できる高効率位相回転ゲート式量子計算アーキテクチャを確立したことを報告した。

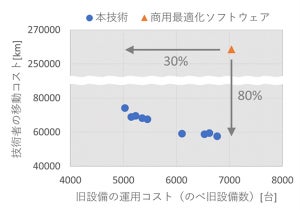

今回確立した量子計算アーキテクチャは、大量の物理量子ビットを使用する論理Tゲート操作を繰り返す従来のアーキテクチャとは異なり、任意の角度を直接指定して位相回転するゲート操作を実行する。これにより、物理量子ビットを従来の10分の1以下に低減でき、任意回転の実行に掛かるゲート操作回数を従来の20分の1程度に低減できるという。

なお、この量子計算アーキテクチャでの量子エラー確率は、物理量子ビットでの量子エラー確率の約8分の1まで抑え込めることを確認しているとのことだ。量子計算アーキテクチャにより、1万物理量子ビットに対して64論理量子ビットの量子コンピュータを構築可能であり、その計算性能は現行コンピュータの最高性能の約十万倍に相当するようだ。

両者は今後について、開発した量子計算アーキテクチャを発展させてEarly-FTQC(Fault-Tolerant Quantum Computation)時代の量子コンピュータ開発を主導していくとともに、材料や金融領域などの実問題への早期適用を目指すとしている。