東京ビッグサイトにて12月14日~16日にかけて開催されているエレクトロニクス製造サプライチェーンの国際展示会「SEMICON Japan 2022」にて、産業技術総合研究所(産総研)が量子コンピュータについての取り組みを紹介している。

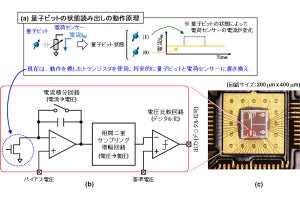

主催者企画である「第3回 量子コンピューティングパビリオン」に設置された産総研のブースでは、スピン量子ビット素子の開発に向け、いくつかのゲートを作製した模擬的な量子ビットウェハや、量子ビット回路と接続して量子ビットを制御することを目的とした量子ビット制御用集積回路試作チップを搭載した4Kで測定可能な評価ボードの実物が展示されている。

これらの研究成果は、科学技術振興機構(JST)が進める「光・量子飛躍フラッグシッププログラム(Q-LEAP)」の基礎基盤研究の1つ「シリコン量子ビットによる量子計算機向け大規模集積回路の実現」によるもの。量子コンピュータのゲート方式としては、超伝導型やイオントラップ型、シリコン型などさまざまな方式が提案されており、世界中でそれらの研究開発が進められている。シリコン型の特徴は、長年培われてきた半導体プロセスが活用でき、それによる大規模集積化によって、高い計算能力を実現できると期待されている点である。また、1K程度での動作も可能であるため、小型化という点でも有利とされている。

ただし、読み出しのための半導体集積回路をそうした量子ビット近傍の極低温環境に置くと、トランジスタの動作特性は室温の状態とは異なったものとなるため、その原理などを理解しないと、正常に動作しない可能性が出てくる。「クライオCMOS技術開発」と呼ばれるこの分野における素子や回路の特性評価に向け、産業技術総合研究所では極低温評価プラットフォームを構築。アジア初(世界で4機間目。先行導入はIntel、仏Leti、Northrop Grummanだという)となる300mm極低温オートプローバの導入など、最先端の測定環境を整備したという。

今回展示されている評価ボードはそうした極低温環境での評価を可能としたものとなっている。

一方の量子ビットとしては、さまざまな形式の素子の評価が2018年より進められてきた。その中で現状、産総研では、Fin型が大規模集積に向くと判断。素子形状としては、シリコン基板に位置整合プロセスを活用し、コバルトの微小磁石を自己整合型プロセスを用いて作製。その上に電極形成層と配線層を形成。自己整合型プロセスを活用すると、電極下部に形成されたスピン量子ビット素子と微小磁石の相対ずれがなくなるため、製造ばらつき耐性を高めることができ、ばらつきによる特性不良が抑えやすくなるという。電極などの形成時の位置誤差が1nm程度でも発生すると性能の劣化が引き起こされるが、産総研が考案した埋込構造では4nm程度までは許容できることが確認されているという。

また、研究開発段階では電子ビーム(EB)を用いているが、最終的な量産に向けてはEUVリソグラフィ技術を活用する必要があるという。EBのスループットがEUVに比べて遅いという部分もあるが、最大のポイントは重ね合わせ精度の高さにあるという。EUVの重ね合わせ誤差(位置合わせの誤差)は3σ値が2nm程度とされており、2nmを超える位置ずれが発生する確率は0.3%。これは1000個に3個の不良が発生する計算で、産総研が考案した構造はその2倍の4nm、これは6σ値となり、その確率は100万個に3個ということとなり、EBではそこまでの精度が現状では出せないためだとしている。

ただし、現状、日本にはASMLのEUV露光装置は1台も導入されておらず、1台あたりの価格も200億円以上と(次世代の高NA対応装置は400~500億円とも)言われているが、年間で生産できる台数に限りがあるため先端プロセス半導体を製造する複数のデバイスメーカー間で取り合いになっている状況である。日本は国として「量子技術イノベーション戦略」を打ち出したり、国家戦略「新たな量子技術に関する戦略:量子未来社会ビジョン」を策定するなど、量子コンピュータ分野で世界をリードすることを目指しているが、その実現に向けては、今後の速やかな研究体制の拡充が求められることになりそうである。