九州大学(九大)と大阪大学(阪大)の両者は12月13日、量子ドット2次元配列における電子スピン制御の実現に向けて、微小磁石が発生させる磁場分布の数値シミュレーションにより、2行2列量子ドット配列用の微小磁石形状設計手法を開発したことを共同で発表した。

同成果は、九大大学院 システム情報科学研究院の木山治樹准教授、阪大 産業科学研究所の中村駿吾大学院生(研究当時)、同・大岩顕教授らの共同研究グループによるもの。詳細は、米国物理学協会が刊行する応用物理学を扱う学術誌「Journal of Applied Physics」にオンライン掲載された。

量子コンピュータを実現するための方式は複数あり、その1つが微小な半導体である量子ドットに閉じ込められた電子スピンを用いる「電子スピン量子ビット」だ。現在、同方式の高精度制御や量子ドット集積化など、基盤技術の開発が急速に進められており、電子スピン制御については、これまでのところ、量子ドット近傍に設置された微小磁石を用いることで高精度制御が実現されている。

また大規模集積化については、量子ビットを2次元的に配列することが重要と考えられており、これまでの研究で、2行2列や3行3列といった量子ドット2次元配列が報告されている。しかし、電子スピン制御方法として有力視される微小磁石を使ったスピン共鳴は、量子ドット2次元配列においてはまだ実現できておらず、電子スピン量子ビット方式での大規模集積化は、あまり進展していない状況だという。

-

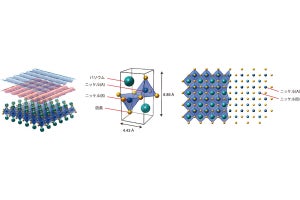

微小磁石を備えた量子ドット2行2列アレイのイメージ。半導体基板(薄オレンジ)の表面にゲート電極(緑色)が作製されており、負電圧を加えることで量子ドットが形成される。ゲート電極の上に微小磁石(黒色)が作製されている(ゲート電極と微小磁石の間の絶縁膜は省略)(出所:九大プレスリリースPDF)

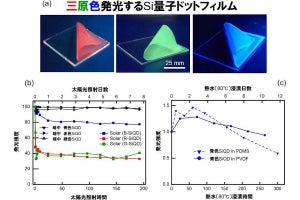

そこで研究グループは今回、微小磁石が発生させる磁場分布の数値シミュレーションを用いて、その設計手法の開発を目指すことにしたとのこと。そして、2行2列量子ドット配列用の微小磁石形状設計手法の開発に成功したとする。この技術では、形状最適化の結果、シリコンを材料とした量子ドットでは精度99%以上が見積もられ、誤り耐性に必要な高精度制御が期待されるとしている。

-

(左)微小磁石の形状。量子ドット位置に生じる磁場分布シミュレーションをもとに、微小磁石形状の最適化が行われた。(右)2行2列量子ドット配列周辺の面内磁場強度分布シミュレーション結果の一例。量子ドット位置は黒丸で示されている(出所:九大プレスリリースPDF)

研究グループは、今回の成果をもとにした量子ドット2次元配列の電子スピン制御の実現と、その後の大規模集積化への展開、そして半導体量子コンピュータの実現に向けた貢献が期待されるとする。

また同グループは今後、得られた設計をもとにした2行2列量子ドット配列用と微小磁石を実際に作成し、電子スピン制御の実現とその精度の評価に取り組むとする。加えて、さらに大きな配列でのスピン制御へと展開し、20~30年後の半導体量子コンピュータの実現を目指すとした。