11月7日に東京で開催された「imec Technology Forum(ITF Japan 2022)」において、ロジック半導体の微細化をさらに進展させるためには、集積システム構成とプロセス技術との同時最適化である「System-Technology Co-Otimization(STCO)」が今後は重要になるとimecのロジックテクノロジー担当バイスプレジデントであるJulien Ryckaert(ジュリアン・リカルト)氏が強調した。同氏にimecで発足したSTCOプログラム発足の背景や狙いについてうかがった。

Julien Ryckaert氏は、2000年にベルギーのブリュッセル大学(ULB)で電気工学の修士号を取得し、2007年にブリュッセル自由大学(VUB)で博士号を取得。2010年にimecに入社し、ADコンバータやRFトランシーバーなどのミックスドシグナル回路設計に従事後、2013年から先端CMOSテクノロジーノード向けの回路設計・プロセス技術同時最適化(DTCO)プラットフォーム構築を担当し、2018年からは3nmテクノロジーノードを超えるスケーリングとCMOSの3D化によるエリアスケーリングに焦点を当てたプログラムディレクターに就任している。

imecが見据える今後の半導体の進化の方向性

-:将来のスケーリング(微細化)技術開発における最大の課題は何だと認識していますか?

Julien Ryckaert氏:現在、半導体業界全体が大きな転換期を迎えています。 10年以上にわたり、ムーアの法則、より具体的にはデナードの法則(MOSトランジスタに関するスケーリング則)に触発された寸法スケーリングは、CMOSテクノロジーノードの将来を予測するバロメーターとして使用できないことが明らかになってきました。

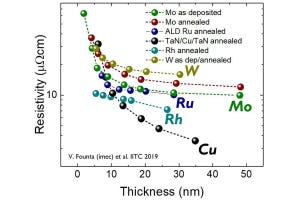

これは、現在「スケーリングの壁」と呼ばれるいくつかの要因に起因しています。CMOSコンポーネントの寸法を縮小することが非常に困難になり、費用がかかるようになっているだけでなく、半導体業界は、複雑なシステムでの電力と速度の深刻な障害に直面しています。

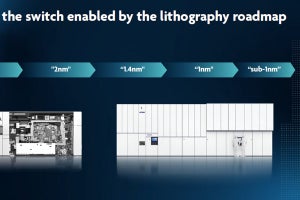

技術レベルでは、回路設計・プロセス技術同時最適化(DTCO)によってサポートされる新しいデバイスアーキテクチャとスケーリングブースターにより、次の2世代のCMOSノードまではある程度の面積スケーリングを維持できます。しかし、ここまでで力を使い果たしてしまうか、少なくとも将来のアプリケーションのシステムスケーリングを提供するのに十分ではありません。アーキテクチャレベルでは、複雑なメモリ階層、マルチコア、マルチスレッド、および単一のSoCまたはチップレットでのコアの特殊化(xPU化)が、これらのスケーリングの壁を克服する方法になっています。

今日、私たちが直面している問題は、これらのイノベーションのほとんどが、真の集積システムアーキテクチャとプロセステクノロジーの同時最適化の結果ではないということです。今後の最大の課題は、主要なシステムスケーリングのボトルネックを解き放つことができる適切なテクノロジー要素を見出すことと、新たなテクノロジーにより新しいコンピューティング方法がどのように可能になるかを探ることです。これが、システム技術共同最適化(STCO)の目的です。

-:imecは今後の課題の克服にどのように貢献しますか?

Julien Ryckaert氏:imecは、もともとエコシステムのテクノロジー側に位置し、エコシステムに真の差別化をもたらしてきました。ただし、将来のテクノロジーを定義する上でリーダーシップを発揮する必要があるため、システムスケーリングに関するテクノロジーロードマップを充実させる必要があります。この進化は基本的に、従来の「汎用」テクノロジーの提供から一歩踏み出して、AI、HPC、AR/VRなどのアプリケーション固有の要件によってソリューションが推進されるという事実を受け入れる必要があることを意味します。

さらに、最適なシステム実装には、極限のCMOSロジックスケーリング、高度な3Dパッケージング、新しいメモリ要素、さらにはシリコンフォトニクスなど、複数のテクノロジーにわたる微妙な最適化が必要です。これらのさまざまな技術研究活動は、これまで別々に実施されており、それぞれに独自のDTCO研究とロードマップがありました。

システム主導のスケーリングへの移行に備えるために、imecが提供するコアプログラムを再編成し、すべてのDTCOアクティビティを1つのプログラムに統合しました。このプログラムは、すべてのコアテクノロジープログラムにわたってプロセステクノロジーから回路設計の最適化までを研究します。このDTCOプログラムを、DTCO研究とシステムを構築する空間との連携を確保するSTCOプログラムで補完しました。このSTCOプログラムの目標は、将来のシステムニーズとボトルネックをトップダウンアプローチでプロセス技術要件に変換することです。また、独自の斬新なプロセス技術機能を活用した新しいアーキテクチャを可能にする可能性も探ります。

-:imecのSTCOはどのような進歩を遂げていますか? 最近の例でそれを裏付けることができますか?

Julien Ryckaert氏:私たちのコアテクノロジー(核となる技術、例えば、ロジック、メモリ、3D実装などの個別技術)プログラムのそれぞれで、すでにある程度のシステム評価が必要な個別の研究活動を開始しました。

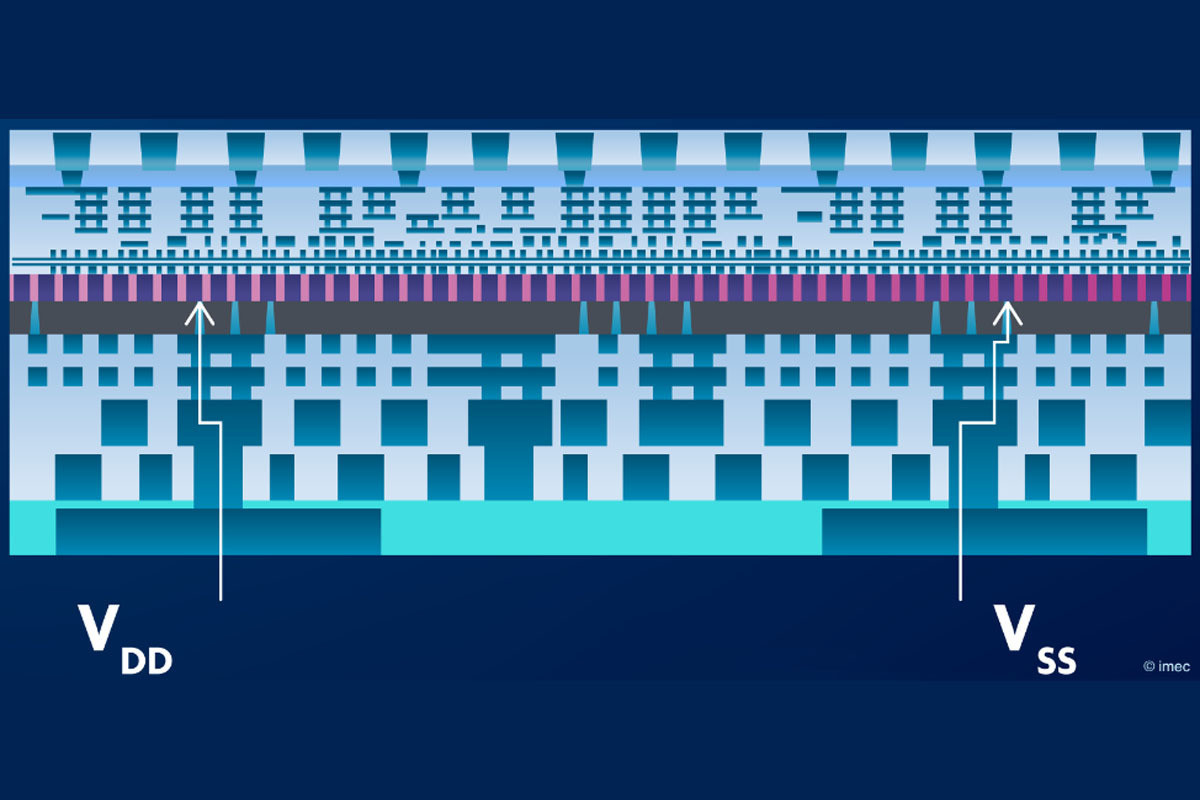

良い例は、2022 VLSIシンポジウムで発表した裏面電源供給ネットワークです。この作業は、3Dプログラムアクティビティとロジックアクティビティが連携して電力供給のシステムソリューションを開発した結果です。裏面技術は、ウェハハンドリングやシリコン貫通ビア(TSV)処理などの3D技術機能を必要とするのと同様に、ロジックスケーリングロードマップに大きく影響します。しかし、裏面電源供給ネットワークが真のシステムパフォーマンスの利点をもたらす理由と方法を理解するには、より複雑な環境での動作を評価し、システム構成を深く掘り下げる必要があります。2021年に、IEEE Spectrumで、imecとArmは、プロセッサ設計レベルでパワーレールを埋め込んだ裏面電源供給ネットワークのシステムレベルの利点を報告しました。

もう1つの例は、オンチップSRAMを置き換えることが想定されている新しいメモリです。このようなメモリソリューションは、必然的にロジックスケーリングのロードマップに影響を与え、システムシミュレーションフレームワークでのみ評価できます。言うまでもなく、これらのメモリのいくつかは3Dで積み重ねられている可能性があります。

これらの例でシステムレベルの課題に取り組み始めるとすぐに、それぞれの例で、すべてのテクノロジーソリューションが互いに絡み合っていることに気付きました。ロジック、メモリ、および3Dプログラムのテクノロジー研究は、もはや個別の「サイロ」(穀物や飼料の機密性を保った貯蔵庫。ここから転じて、組織間の情報共有や風通しが悪く組織運営が非効率な様の比喩)で処理できないことが明らかになりました。これらの研究は同時に実行され、システムアプリケーションが最適になるようにしなければなりません。システムの観点から分析された多くの研究活動がすでに存在するため、ゼロから始めなければならないわけではなかったことはよかったです。

-:今後数か月で何が期待できますか?

Julien Ryckaert氏:私たちは、新しいDTCO/STCOプログラムのセットアップを研究契約パートナーに発表したばかりで、今後6か月間の一連の成果予測を配布したところです。これらは、システムのスケーリングに不可欠な3つの壁、つまり、

- メモリ/帯域幅の壁(ロジックコアに供給するのに十分な速度でデータを取得する方法)

- 電力/熱の壁(電力供給と熱放散を効率的に処理する方法)

- 寸法スケーリングの壁

に関連しています。

もちろん、この研究ロードマップをパートナーと調整し、業界にとって適切な課題に取り組んでいることを確認する必要があります。これには、すべてのパートナーとの綿密な話し合いが必要であり、これらはすでに開始しています。

-:このプログラムを設定する上で、imec が世界の半導体業界で優位な理由は何ですか?

Julien Ryckaert氏:真のSTCO研究には、多くの分野を統合する必要がありますが、それぞれの分野が大きく異なるスケールを扱い、抽象化の異なるドメインで独自の科学を適用しています。

真の課題は、途中で重要な情報を失うことなく、あるドメインから別のドメインに適切な抽象化レイヤのセットを構築することです。これは、完全なシステム最適化を実行するために情報を上から下へ、下から上へ伝達する唯一の方法です。

これを適切に行うには、各ドメインで適切な専門知識が必要なだけでなく、これらの分野が互いに密接に相互作用する必要もあります。imecは、これらの分野のほとんどが同じ屋根の下にあり、密接に連携している独自のインフラストラクチャを保持しています。これにより、アイデアの交換、情報の円滑な伝達、および結果と解釈に対する批判的な視点の拡大が促進されます。すべてのコアプログラムにおいて、このSTCOが前進することに大きな期待感があります。どの分野の出身であっても、半導体研究の将来に変化をもたらすにはSTCOフレームワークが必要であることを誰もが理解しているからです。imecは、そのようなイニシアチブを開始するのに最適な場所だと思います。