Samsung Electronicsは10月18日、都内にて「SFF(Samsung Foundry Forum) 2022 Japan」を開催した。2020・2021年はCOVID-19の関係で開催できなかったため、3年ぶりの開催となる格好だ。このSFF 2022 Japan開催に合わせて、Samsung ElectronicsのMoonsoo Kang氏(EVP, Head of Foundry BusinessDevelopment Team)による記者説明会が開催されたので、こちらをご紹介したい。

まず市場動向について。登壇したChun氏によれば、半導体ビジネス全体のマーケットは2010年の3110億ドルが2020年に4710億ドル(CAGR 4%)、2026年には7830億ドル(CAGR 9%)となっているのに対し、ファウンドリビジネスは2010年の320億ドルから2020年に760億ドル(CAGR 9%)、2026年には1500億ドル(CAGR 12%)と半導体ビジネス全体に比べるとより高い成長が見込める、としている。

ではSamsung Foundry自身は? というと、明確な数字は示されていないが、2021年に比べると2027年は売り上げが3倍ほどになる事を予測しており、またアプリケーション別で言えば、Mobile/HPC&Automotive/Consumerの3つの柱の中で2019年だと大半がMobileだったのに対し、2022年ではHPC&Automotiveが2019年比で2倍、2027年には3.5倍に伸びる、と予測している。

顧客別で言えば、特に自動車業界のADAS向けが大きく伸びるが、それはともかくとして全体として2027年には2019年比で5倍以上の顧客が獲得できるとし、また地域別売上高で言えば米国とEMEAが2019年比で12倍、アジアは6倍になると予測している。ただ地域別の売上高はいろいろムラがあり、米国とアジアはそれなりにMobileが強いが、今後はHPC向けが大きく成長すると予測する一方、EMEAではConsumer向けが大きく伸び、次いでAutomotive向けが伸びるとしている。

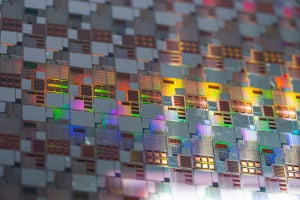

さて、そんなSamsung Foundryの現在のロードマップがこちら(Photo01)。

2021年時点でのロードマップはこちらにまとめたが、まず今年は大きく名称が変更になった。今までは5LPPとか3GAEといった、プロセスノード+特徴をまとめた物が、今回からSFxxという名前になった。恐らく他のFoundryのプロセスと明確に区別するためと思われるが、ただSF4の系列は正直判り難い。

小さく記されているが、

- SF7 :7LPP

- SF6 :6LPP

- SF5E:5LPE

- SF5 :5LPP

- SF5A:5LPE-A

- SF4E:4LPE

- SF4 :4LPP

- SF4P:4LPP+

- SF4X:4LPC

- SF4A:4LPA

- SF3E:3GAE

- SF3 :3GAP

- SF3P:3GAP+

とそれぞれ読み替える形だが、5LPE-Aとか4LPAなど、これまでなかったプロセスがだいぶ湧いている格好だ。

今年6月末に同社はSF3E(3GAE)の量産開始をアナウンスしており、また今月3日に行われたSFF&Safe Forum 2022では2nm/1.4nmのアナウンスを行っており、これがロードマップにも反映されている。

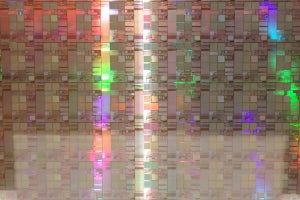

同社はまたイメージセンサやeNVM、HV(High Voltage)やRFなどについても、今後積極的にプロセスの微細化を進めてゆく(Photo02)としている。

-

Photo02:これを見て“もう18nm FD-SOIは止めたのか?”と確認したところ“18nm FD-SOIはStrategic Customer向けのカスタムプロセスで一般提供はしない”との事。28nm FD-SOIを使っているNXPやLattice Semiconductorなどは今後どうするのだろう?

さらに自動車向けについては、ISO 26262やIATF 16949、AEC-Q100などに準拠したプロセスとして現在14LPUや8LPP/SF5A、および28nmのeFlashを提供しているが、2024年第1四半期には14LPU eMRAM、第4四半期にはSF5A、2025年第1四半期にはSF4Aをそれぞれ投入予定とした。

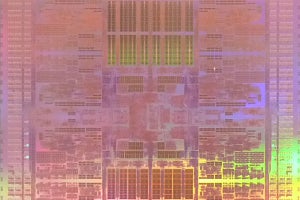

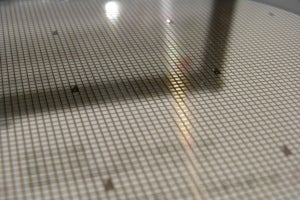

加えて、今後はMature nodeの生産能力拡大も進めてゆくとしており、具体的には8nmノードに関して2023年末までに2019年比で1.5倍まで生産能力拡大を行ってゆく、としている(それ以外のMature Nodeに関しても能力拡大が行われる模様)。この生産能力拡大のキーとなるのが製造施設の拡充である。同社は韓国に3か所の拠点を開設しているが(Photo03)、これに加えてテキサス州に新Fabを立ち上げる事を昨年11月に発表しており、2024年後半に稼働を開始する予定である(Photo04)。

以上が今回のおおむねの発表内容であるが、補足を1つ。パッケージング技術として、同社は2.5DのSilicon InterposerをI-CubeおよびH-Cubeとして発表しており、これに続く3D StackingをX-Cubeとしてすでにアナウンスしている。これは要するにTSMCのSoICとかIntelのFoverosと同じ技術であるが、SoICだとGraphCoreのBow IPU、FoverosだとIntelのMeteor LakeがいずれもLogic/SRAMの積層ではなくPower Delivery用のSilicon Capacitor向けにこれを利用している。一方でX-CubeはLogic同士の積層を想定している訳だが、同じようにPower Delivery用に利用可能か? と確認したところ、そうした事は可能ではあるが、その目的にはSilicon Capacitorを積層する別のStacking Solutionがある、という返事であった。ちなみにX-Cubeの量産開始は2024年だそうである。