NTT、九州大学(九大)、東京大学(東大)、科学技術振興機構(JST)の4者は9月30日、量子コンピュータの動作に応じて動的に誤り訂正を行うことで、誤り耐性量子コンピュータの拡大における障害とされてきた「バーストエラー」の影響を削減するアーキテクチャを提案したことを発表した。

同成果は、NTT、九大、東大の共同研究チームによるもの。詳細は、IEEE主催の国際会議「The 55th IEEE/ACM International Symposium on Microarchitecture(MICRO-55)」にて10月1日に発表された。

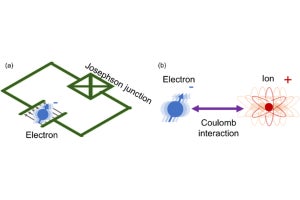

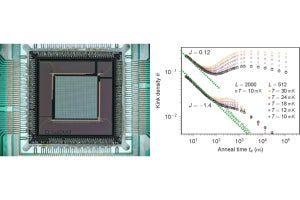

量子ビットは環境ノイズに脆弱であるため、たとえば超伝導回路を用いた量子ビットでは、宇宙線の照射により、広範な領域の量子ビットのエラー特性が数十ミリ秒間変化することが報告されている。こうしたバーストエラーへの対策技術も開発されているが、デバイス開発に大きな制約を与えるものしかなく、今後の実装における大きな課題となっていたという。

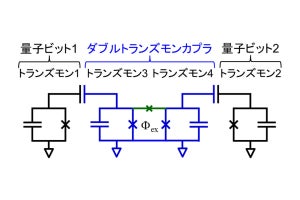

そこで研究チームは今回、バーストエラーの影響を大幅に削減する量子コンピュータのアーキテクチャを提案することにしたという。そして、量子コンピュータを制御する古典コンピュータの制御機構に追加の論理ユニットを加えることで、超伝導量子ビットにおいて宇宙線により生じる同エラーの持続時間や影響範囲を大幅に抑えられることを示せたとする。

今回の核となる技術は、「異常検知」、「動的な符号方式の変形」、「エラー推定の再実行」の3つ。異常検知技術によってバーストエラーの発生を短遅延で検出することになるが、直接測定では量子ビットが壊れてしまうため、同エラーの発生もエラー頻度を直接観測で調べることはできない。そこで今回は、エラー推定のヒントとして使われるパリティ値の統計的なふるまいから、同エラーの発生を検知するとした。

バーストエラー発生が検知された場合、その軽減のための2つの手続きが実施される。1つは、符号方式の変形による同エラー対策で、エラーが検知されたら、効率は悪いがエラー耐性のある符号方式に即座にスイッチすることで、検知以降の同エラーの影響をほとんどゼロにできるという。今回は、そうした割り込み処理を小さなオーバーヘッドで行うための機構が提案された。

もう1つは、バーストエラー情報を用いたエラー再推定だという。推定を行う論理ユニットは古典コンピュータであるため、十分な情報があれば同エラーが到着する前まで状態を巻き戻し、「バーストエラーが生じている」という情報に基づき、より正確なエラー推定を行えるようになることから、これにより同エラーが生じてから検知されるまでの間に生じる影響をさらに軽減することが可能だという。