Hot Chips 34においてNVIDIAは新GPU「Hopper」を発表した。NVIDIAはデータのローカリティを改良したり、助け合うような実行を行うことで性能を高めたり、実行とデータ転送を非同期で実行するなどの改良を行ったとしている。また、ディープラーニングの性能を加速することも行うなど、各種の改良が行われているが、今回は、中身が専門的で説明が難しいものは省略させていただく。

-

図1 Hopperでは、データローカリティの改善や実行と転送の非同期の実行などの原理的な性能改善を行った (このレポートのすべての図は、Hot Chips 34でのNVIDIAの発表資料のコピーである)

NVIDIA H100 Tensor コア GPUはTSMCの4nmプロセス(N4)で作られ、800億トランジスタを集積している。H100は132SMを搭載し、クロックあたり132SM×2の性能を持つ。第4世代NVLinkをサポートし、900GB/sのトータルバンド幅を持つ。そして新しいSHARP機能を備えスイッチ部のネットワーク処理機能をポートに内蔵する。

L2キャッシュはHBM3で作られている50MBのキャッシュであり、第2世代のMulti-Instance GPUは暗号化処理を行う機能を持っている。

HopperのSM(streaming multiprocessor)はFP32とFP64のFMA演算性能はA100の2倍の性能になっている。L1キャッシュやShared Memoryも倍増されている。そして、テンソルコアは第4世代となり、アップグレードされており、DPX命令セットが更新され新しいテンソルメモリアクセラレータは完全に非同期にデータを移動することができる。そして、新しいスレッドブロッククラスタはローカリティを実行効率の改善に利用できるようになったという。DPX命令はダイナミックプログラミングの命令のようであるが、説明が無く、どのように使われるのか良く分からない。

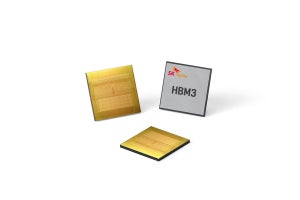

HBM3メモリをGPUで用いたのはHopperが最初である。これにより、メモリのバンド幅は3TB/sに向上した。右側の棒グラフのように、A100では1.7TB/sのメモリバンド幅であったが、Hopperでは3TB/sと大きく向上した。

また、新しいDRAMコントローラは2倍のチャネル数を持ち効率が改善している。

-

図5 MIG(Multi Instance GPU)の計算性能は3倍、メモリバンド幅は2倍。MIGごとにイメージやビデオのデコーダを持ち、TEE(Trusted Execution Environment)を備え、MIG間の分離を強化している

H100+NVLink NetworkではHPCやAIの処理性能が改善している。特にセンターで推論を中心に処理を行う場合はA100をH100に変えるだけで短レーテンシで大量の処理ができるようになり、効果的だという。

第4世代のHopper Tensorコアは同じクロックでの性能が2倍に向上している。そして、FP8フォーマットが新たにサポートされた。

H100の性能向上はTensorコアとFP8のサポートの効果が大きい。

テンソル演算については、8bitのFP8の演算をサポート。8bitの演算にすればBF16やFP16などの2倍の演算が出来るようになるが精度や数値範囲が不足するという問題がでる。それを解決するため、NVIDIAは数値範囲を優先する「E5M2」という形式の表現と数値の精度を優先する「E4M3」という数値表現を作り、2つの数値表現を切り替えて使用するという方法を工夫した。

そして、テンソルエンジンの動きをモニタしていて、この2つの数値形式のどちらを使うかを自動で切り替える。図12の表をみるとこの切り替えはうまく行っているようである。

-

図11 HopperのテンソルコアのFPトランスフォーマエンジンは、統計値をモニタしてどちらのFP8フォーマットを使うか選択する。人間が命令で切り替えることもできるので、自動切り替えが上手くいかない場合は人手で切り替える手もあるかも知れない

次の表は、FP8を使った場合の学習精度を示す。FP8を使った場合の方がFP16より誤差が小さいケースもあり、典型的な結果である。

-

図12 最後から2列目の16-bitでのaccuracyは、最後の列のFP8のaccuracyとほぼ同じで、FP8での学習ができることを示している。また、右側のGPT-3の学習もうまく行っていることを示している

DGX H100 Superpodは32台のDGX H100ノードをまとめたもので、AI計算では1ExaFlopsの演算性能を持つ。ネットワークのBi-Sectionバンド幅は70.4TBとなっている。

-

図13 DGX H100 Superpodは32台のDGX H100ノードをまとめたもので、H100 GPUを256コア使用し、164個のNVLink4で相互接続を行っている。ピークAI演算能力は1ExaFlopsに達する

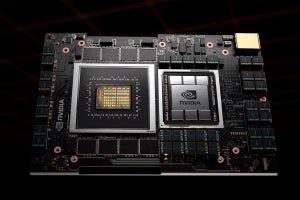

なお、NVIDIAのGrace Hopperスーパーチップでは、NVIDIA Grace CPUとH100は毎秒900GBの通信バンド幅を持つチップ間インターコネクトで接続され、このバンド幅はPCIe Gen5の7倍のバンド幅である。