産業技術総合研究所(産総研)、NTT、科学技術振興機構(JST)の3者は6月30日、電子回路ではなく、シリコン光集積回路を使った超低遅延かつ低消費電力のニューラルネットワーク演算技術を開発したと発表した。

同成果は、産総研 プラットフォームフォトニクス研究センターのコン・グアンウエイ主任研究員、同・山田浩治総括研究主幹、NTTの共同研究チームによるもの。詳細は、英オンライン科学誌「Nature Communications」に掲載された。

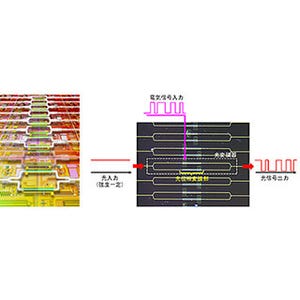

AIの処理システムは年々、大規模化が進んでおり、その結果として生じている電力消費量の増大、演算遅延の問題などの解決が求められるようになっている。そうした手法の1つとして、デジタル演算のようなデバイスのスイッチングが不要なために消費電力が少なく、光が伝搬する時間で演算を完了できる光集積回路を用いた光ニューラルネットワーク演算によるAIアクセラレータが期待されている。

しかし、現在の技術では光を用いた非線形性応答デバイスの集積が困難なため、光信号を電気信号に変換する必要があり、光集積回路だけでニューラルネットワーク演算を実現することができていなかった。また、光演算回路の学習は、コンピュータによる事前学習が主流であるが、自らの経験に基づいた自律的な学習に向けては、回路実機に対する直接学習が必要とされているという。

そこで研究チームは今回、光干渉計デバイスの駆動電圧に対する非線形性を用いるために、データ入力部の光干渉計デバイスにより、解析すべきデータを高次元光複素振幅空間に非線形写像し、さらに多数の光干渉計から構成される光集積回路に光伝搬させることにより演算結果を得るという非線形写像型のニューラルネット演算方式を提案したとする。