6月13日から17日にかけてハワイで開催され、オンデマンド放送も行われている「2022 IEEE Symposium on VLSI Technology&Circuits(VLSIシンポジウム)」にて、imecは、15件の論文が採択されたほか、招待講演1件の発表を行ったことを明らかにした。また、このほか、複数の特別企画に研究者が招待され、登壇したともしている。

発表された論文15件は、ロジック回路およびメモリ技術とアプリケーション、高度な相互接続、無線技術、および生物医学システムなどの幅広い分野にて採択されたものとなっている。

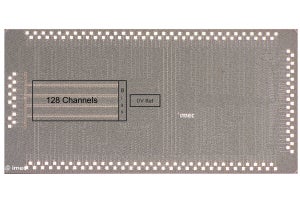

具体的にはどのような内容か、別途記事としている小型、低ノイズ、低電力な神経インタフェースを実現する128ビット神経読み出しマイクロチップ技術を除いた15件をテーマ別に紹介する。

招待論文

- ワイヤレス異種統合:ロジック回路微細化関連

- 埋め込み電源配線(BPR)を介したウェハ両面配線を持つ微細FinFETプロセス(VLSIシンポジウムプログラム委員会推薦注目論文)

- サブ2nmノードでの2Dおよび3D ICのIRドロップを改善するためのダブルブーストとしての裏面PDN(電力供給ネットワーク)および2.5D Mimcap(金属-絶縁体-金属コンデンサ)

- 18nmメタルピッチでの完全自己整合ビアを備えた2つの金属レベルのセミダマシン相互接続のデモンストレーション

- 16nmの金属ピッチを備えた4トラック設計用のシートベースのCFET構成のPPAC(電力・性能・面積・コスト)

- iN8-iN2(8~2nm)CMOSロジックセルの自己発熱:FinFET/ナノシート/フォークシート/CFETなどのアーキテクチャとスケーリングブースターの熱的影響

- 低温Si層転写と層相互接続を用いた最上層デバイス製造を特徴とするCMOS FinFETスタッキングでの3DシーケンシャルFD-SOIのデモンストレーション

- DTCO/STCO(設計・技術およびシステム・技術同時最適化)でのESDおよびLUの信頼性のためのアクティブバックサイドテクノロジーの有効化

イメージセンサ、メモリ、新規デバイス関連

- コロイド量子ドットイメージセンサのウェハレベルピクセル化

- 高性能耐熱FinFET:Vth調整可能性を備えたDRAMペリフェラルCMOS FinFET

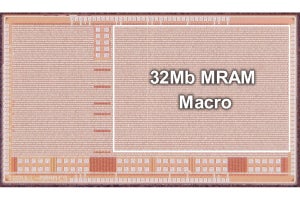

- 高密度および低電力の組み込みメモリ用のマルチピラーSOT-MRAMの選択的操作

- バイポーラモードで動作するSiGeAsSe-GeSbTe 1S1R相変化メモリのパフォーマンスと低電力機能

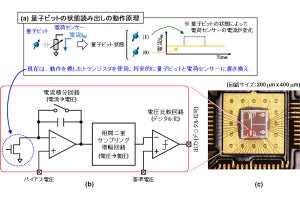

- 高忠実度の超伝導キュービット測定のために10mKで動作するスケーラブルな1.4μWクライオCMOS SP4Tマルチプレクサ

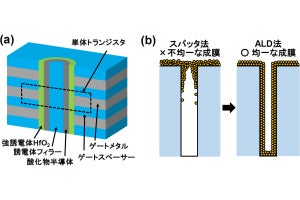

- PVとIVの同時測定による強誘電性Hf0.5Zr0.5O2 pFETとnFETのデータ保持損失への洞察

- せり上げソース/ドレインのある超低リークIGZO-TFT:Vt>0V かつ Ion>30μA/μm)