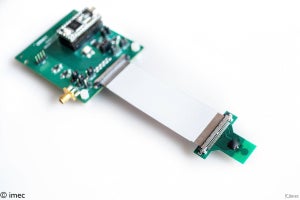

ベルギーimecが、「2022 IEEE VLSI Symposium on Technology and Circuits(VLSIシンポジウム)」にて、神経生理学実験における局所電位と活動電位の同時取得のための小型記録チャネルを備えた、神経読み出しマイクロチップを発表した。

同チップは、新開発のAC結合1次Δ-ΔΣアーキテクチャに基づいており、弱いアナログ信号源のごく近くで直接デジタルドメインへの変換を可能にしたもの。低電力と小面積は、高チャネル数のニューラルインタフェース向けICの設計課題とされてきており、imecでも、ノイズ、電極DCオフセットキャンセル、入力範囲などの他のメトリックで良好なパフォーマンスを維持しつつ、そうした要求を満たすことを目的として複数の読み出しアーキテクチャの調査を進めてきたとする。

実際に、すべてのメトリック間のトレードオフを実現するのは簡単ではないが、さまざまな試行錯誤の結果、従来の最新のNeuropixelsの設計と同等またはそれ以上のノイズ、電力、および面積のパフォーマンスを実現すると同時に、AC結合されたΔ-ΔΣ変調器によりダイナミックレンジと電極のDCオフセット許容値を向上させるデジタル集約型ニューラルレコーディングICを開発することに成功したとする。

「我々の設計は、AC結合と直接デジタル化を組み合わせて、レールツーレールDCオフセットキャンセルと他のAC結合設計よりも高い入力範囲(43mVpp)を実現することに成功した。これは、記録チャネルの飽和を防ぎ、起こりうる動き/刺激アーチファクトを許容するために不可欠である。AC信号のみがデジタル化されるため、AC結合入力ステージは消費電力(チャネルあたりの合計8.34μW)をさらに削減する」とimecのCircuits for Neural Interfaces TeamのチームリーダーであるCarolina Mora Lopez氏は説明している。

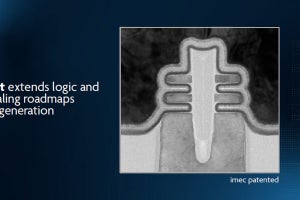

なお、今回開発されたΔ-ΔΣアーキテクチャにより、デジタルドメインでの機能の大部分(アンチエイリアシングフィルターなど)の実装が可能になるとのことで、22nm FD-SOIの利点を活用することで、チャネル領域全体(0.005mm2)を縮小し、信号品質を向上させることができたことから、Carolina Mora Lopez氏は「このスケーラブルなデジタル集約型の設計により、神経信号の同時取得に優れたパフォーマンスを備えた、フットプリントが小さく低電力のICが実現できるようになる。これにより、神経科学研究を前進させる、より高い電極密度を備えたさらに小さなプローブへの道が拓けた」と結論付けている。