ベルギーの独立系先端半導体研究機関であるimecは、2022年5月17~18日(欧州時間)にアントワープで開催した年次技術発表イベント「Future Summits 2022」(6月1日時点では、有料オンデマンド放映中)で、14年後の2036年に2Å(オングストローム)に至る半導体プロセスの微細化ロードマップを発表した(図1)。

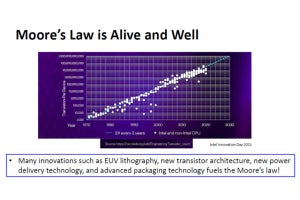

imecは、(1)蘭ASMLと共同開発を進める新しい半導体露光技術(高NA EUVリソグラフィ)、(2)革新的な半導体デバイス構造/構成材料、(3)相互配線層構造などを組み合わせることで、微細化の限界を突破し、「ムーアの法則は2036年まで継続できる」との見通しを示した。これらの要素技術の極めて初歩的な試作検討を経て技術開発のめどが立ったため、ロードマップを1nm(10Å)を超える段階へと更新したようである。

-

図1 imecの新しいロジックデバイスロードマップ。上から西暦、技術ノード名(Nはnm、AはÅを意味する)、寸法縮小の指標=メタル配線ピッチ(nm)、デバイスと材料革新の指標=メタルトラック数、トランジスタ構造、微細化に適合した相互配線の構造 (出所:imec、以下すべて)

EUVリソグラフィの進化

imecは、Beyond 2nm(2nmを超えた微細化)には高出力かつ高開口数の「High-NA EUV露光装置」が必要であり(図2)、唯一のサプライヤであるASMLと「imec-ASML High-NA Lab」を共同設立して実用化研究に取り組んでいるという(図3)。

開口数NA=0.33の従来タイプのEUVリソグラフィは、試作機出荷(2010年)から量産機出荷(2019年)まで約10年かかったが、NA=0.55の高NA EUVリソグラフィでは、試作機出荷(2023年)から量産機出荷(2026年)まで3年に短縮して見せるとASML/imecは強気の姿勢を見せる。

デバイス構造の進化

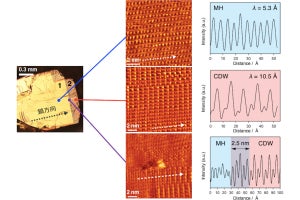

デバイスの微細化は、リソグラフィだけに依存しているわけではなく、トランジスタをより微細化に適した専有面積を縮小した構造にすることによっても実現してきた(図4)。これらを踏まえてimecが更新したロジックデバイス微細化の詳細なロードマップを見ると、現状の「FinFET」は2nm技術ノード以降はチャネルをゲートで完全に取り囲む次世代トランジスタ「ナノシートGAA(Gate-All-Around)」に代わる。さらには1nm(10Å)世代になると、フォークの形をした「フォークシートGAA」(図6)、さらには5Å世代には「CFET(Complementary FET)」へと進化する。そのころになると、トランジスタ内のチャネルに高移動度の単原子層二硫化タングステン(WS2)などの2D材料が適用されることが想定されている(図7)。

多層配線構造の進化

プロセスの微細化、トランジスタの高集積化に対応して多層配線構造も大きく変わる。これまでトランジスタの上部に多層配線層を形成して電力を供給していたが、集積度が高まるにつれてこれらの電力供給配線網が回路の微細化の妨げになっていた。このため、電力供給を裏面側から行うことで、前面側の配線設計の柔軟性を高められるようにするという(図8)。この手法はすでにIntelが採用を発表している。イメージセンサ(CIS)も以前は、配線層と画素が同居していたが、配線層を下部に分離することで画素の面積を拡大し感度を向上させたのと同じ発想である。

3次元実装によるムーアの法則の継続

これまで取り上げたのは、2次元の縮小により集積度をあげる手法だが、複数の異種チップを積み重ねるヘテロジニアスインテグレーションである「3次元実装」により、単位面積当たりの集積度を何倍にも上げることができるようになる。例えば、BS-PDN(裏面電源供給ネットワーク)ロジックデバイスの上にSRAMを積層したヘテロジニアス・インテグレーション3DコアプロセッサSoCの断面模式図とチップ間接続部分の断面TEM像を見ると、チップ間を上下で相互接続することでチップ間の高速通信や省電力化が可能になることが見てとれる。

なおimecは、プロセス技術、回路設計、システム設計まですべてを同時最適化する「システム思考(system-level thinking)」で微細化の限界を乗り越え、新しい破壊的な革新が可能になるとしており、ムーアの法則を今後15年以上継続させるとしている(図10)。

服部毅

202年6月3日訂正:記事初出時、SEM画像と表記しておりましたが、TEM画像であったことから、当該部分を訂正させていただきました。ご迷惑をお掛けした読者の皆様、ならびに関係各位に深くお詫び申し上げます。