Cool Chips 25でIntelのDebendra Das Sharma氏は「Universal Chiplet Interconnect Express(UCIe)」に関する発表を行った。

1965年のElectronics誌にMoore氏は「大規模なシステムは別々のパッケージに入れた小さな機能を接続して作り上げる方が経済的になる可能性がある」と書いている。

-

図1 1965年にMoore氏は、大きな機能は小さな機能を配線でつないで作る方が経済的になる可能性がある。と書いた (このレポートのすべての図はCool Chips 25におけるIntelのDebendra Das Sharma氏の発表スライドのコピーである)

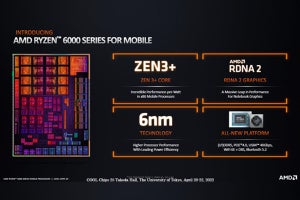

LSIの開発コストは、図2に示すように微細化につれて急激に高くなっている。プロセスが微細になると、集積されるトランジスタの数が増え、設計も複雑になる。また、トランジスタや配線が微細になると加工費も高くなる。結果として、65nmプロセスのLSIの開発費は2850万ドル程度であったのであるが、先端の5nmプロセスのLSIの開発費は5億4220万ドルに跳ね上がっている。

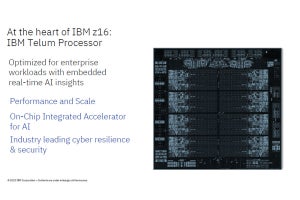

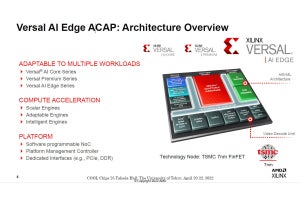

そのため、最先端のプロセスを使わなくても済む部分には、多少微細度が劣るプロセスを使う方が安上がりになるという考えが出てくる。したがって、微細度は最先端ではないが多くの用途に使える部品を多種類用意しておき、それらの中から必要な部品を選択して配線で接続するだけで新たなLSI部品を開発しなくても所要の機能を持つ部品が作れるようになる。

各種のLSI部品を開発し、色々なユーザが使えるようにしておく必要があり、コストも掛かるが、ユーザが多くなれば安くなって行き、先端プロセスを使ったり、大きな単一チップを作るよりも安くなると考えられる。

AMD、Arm、Intel、Qualcomm, Samsung、TSMCなどのチップ設計会社、パッケージングを行うASE、そしてGoogle Cloud、Meta、Microsoftなどのクラウドサービスの提供会社がUCIeの推進メンバーに名を連ねている。