2022年4月20日(水)から22日(金)の3日間にわたって、東京大学(東大)浅野キャンパスの武田先端知ビル5Fの武田ホールにおいて25回目となるCOOL Chips(COOL Chips 25)が開催される。

COOL Chipsは8月にStanford大学などで開催されるHot Chipsの姉妹学会で、集積回路関係の論文を中心に多くのインターナショナルな論文が発表される。歴史的には、横浜の情報文化ホールで開催していたが、最近は新型コロナの影響で開催がリモートになったりしていた。

しかし、今年は武田ホールでのリアル開催とオンラインの両方のハイブリッド開催という形式になる。

COOL Chipsは、論文は英語であるし、質疑も英語であるので、若い学生さんが国際学会出席や発表の練習を行うという点でも都合の良い学会であると思う。

初日の午前中は、シカゴ大のFred Chong教授の招待講義と中央フロリダ大のYan Solihin教授の招待講義である。Chong教授は、ハードとソフトのコデザインで量子アルゴリズムとマシンの間のギャップを縮めるという講義である。量子ゲートレベルで無く量子素子レベルでプログラムを書けば、効率の良いプログラムを作れるという話は、目から鱗と言う感じである。現状では、Solihin教授の招待講義のタイトルは後日発表となっている。

そして、初日の午後は3つの基調講演が行われる。最初の基調講演はIntelのDebendra Das Sharma氏の講演で、Universal Chiplet Interconnect Expressについての講演である。複数の小さなチップを相互接続して高性能のチップを作るChiplet実装は流行りであり、面白そうな基調講演である。

2番目の基調講演はNSITEXEのShotaro Shintani氏の講演でRISC-Vの並列プロセサIPについての発表である。

3番目の基調講演はNanoBridge SemiconductorのMakoto Miyamura氏の発表で、ナノブリッジという抵抗値がスイッチする配線を作り、宇宙機器向けのFPGAを作るという話である。

また、1日目の最後にはポスター発表が行われる。

2日目は開会の挨拶に続いて、IBMのChristian Jacobi氏の「The IBM Telum enterprise-class processor」という基調講演が行われる。TelumはIBMの次期ZプロセサとLinux OneプロセサのCPUチップとして使われると発表されている。Telumは昨年8月に概要が発表されているが、次回のCOOL ChipsでTelumのアーキテクトに直接質問すれば、新しい情報が聞けるかもしれない。

その次はeSOLのMasaki Gondo氏が組織するパネルディスカッションで、高性能組み込みシステムの将来像をパネリストが討論する。

その次の基調講演はIntelのJoseph Curley氏とTimothy Mattson氏が1つのAPIで多種のハードウェアを動かすOneAPIについて講演する。OneAPIで複数のハードウェアを並列に動かすことは可能と思うが、筆者には並列動作でチップの使用率が上がる以外に、どういうメリットがあるのか良く分からないので、注意して講演を聞いてみたい。

昼休みの後は、パワーマネジメントのセッションで、第1著者は東大のTakuya Kojima氏であるが、著者には国立シンガポール大の奥原氏、慶應義塾大(慶応大)の近藤教授や天野教授も入っている論文で、Convex最適化でボディーバイアスを調整するという発表である。

続いて慶応大のIizuka Kensuke氏が第一著者で、天野教授のグループのメンバーによる直接接続したFPGAクラスタの消費電力の解析という論文が発表される。

それに続くセッションVIの基調講演は、ソフトウェア定義のアーキテクチャとプラットフォームという題でeSOLのMasaki Gondo氏が講演する。さらに16時10分からの回路ベースのマシンラーニングのセッションではNAISTのReon Oshio氏が第一著者の論文が発表される。Memcapacitiveなスパイク型のニューラルネットワークについての論文のようである。

2日目最後の発表はETH ZurichのMoritz Scherer氏等の論文発表で、TinyMLのアクセラレータで1036Top/s/W、12.2mW, 2.72μJ/Inferenceの性能を得たという発表である。

最終日の4月22日は、最初の招待講演でAMDのRyzen 6000シリーズについてJim Gibney氏が発表する。

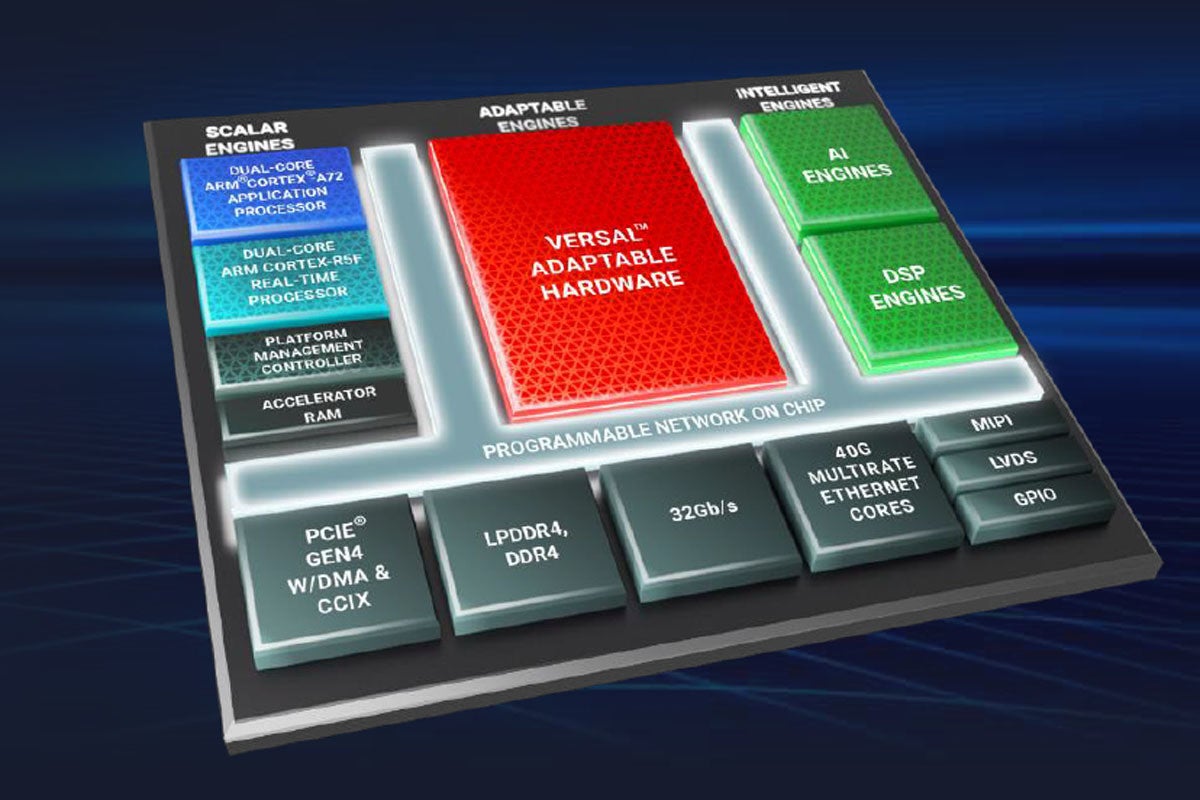

続く基調講演はXilinxのJuanjo Noguera氏がXilinxの7nmエッジプロセサについて講演する。

10時40分からはMachine Learning IIのセッションで、最初の論文は強化学習を使ってマッピングを行うというもので、著者はインド工科大のShine Parekkadan Sunny氏とSatyajit Das氏である。

次の論文は韓国のKAISTのDongseok Im氏らの発表で、低電力で3Dのオブジェクト認識を行うプロセサに関する発表である。そして、京都工繊大のYuki Abe氏等はFiCC memoryを使う間欠動作を行うプロセサを発表する。さらに、マルチプロトコルの工業用無線通信機に関するUCAS(University of Chinese Academy of Sciences)のYang Chen氏等の論文、パラレルビデオエンコーディングを行う際の効率の高いリファレンスイメージの分配に関するNTTのKen Nakamura氏等の論文、超低レーテンシの8Kビデオの伝送システムに関するNTTのYasuhiro Mochida氏等の論文が発表される。

次のドメインスペシフィックなアクセラレータのセッションでは、多数のシグネチャの生成や認証処理のアクセラレーションに関する東大のKaoru Masada氏等の論文、FPGAを使う多数パターンのマッチングを行う方式に関するベトナムのLe Quy Don Technical UniversityのHoang-Gia Vu氏の論文が発表される。

そして、最後に優秀ポスターの表彰が行われる。

ポスター発表は、Times Higher Educationの評価値などに頼って申し訳ないが、スイスのETH Zurich、インドのIIT、シンガポールのNSU、韓国のKAISTなど高い評価の大学による発表が増えており、COOL Chipsの論文の質が上がっている感じがする。