新エネルギー・産業技術総合開発機構(NEDO)、産業技術総合研究所(産総研)、東京大学の3者は3月22日、エッジ向けAIチップの設計を中小・ベンチャー企業などでもコストを抑えて容易に行えるようにするため、AIチップに使用するAIアクセラレータの開発を目的として構築が進められている評価プラットフォーム用実証チップ「AI-One」を用いて、仕様が異なる6種類のAIアクセラレータを1チップ上に搭載し、評価を行った結果、設計通りの周波数での動作を確認したと発表した。

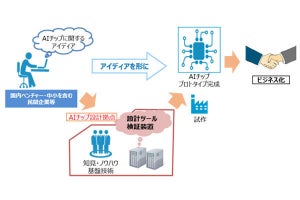

現在、AIチップに限らず、高性能ロジック半導体の開発における障壁として、半導体設計に高度な技術が必要なことに加え、高額な回路設計ツール、検証装置などをそろえる必要があるという点があり、良いアイデアを有する中小・ベンチャー企業などが、実際にチップ化することが難しい状況にあるという。

こうした状況の打破に向け、NEDOは「AIチップ開発加速のためのイノベーション推進事業」を2018~2022年度にかけて実施している。産総研、東大と共同で、東大 浅野キャンパス内にAIチップ設計拠点を設置し、半導体設計に必要な共通基盤技術の開発や回路設計用のEDAツール、標準IPコアなどからなる設計環境の整備が進められてきており、中小・ベンチャー企業などが開発する独自のAIアクセラレータ向け評価プラットフォームの構築もそうした取り組みの一環として進められてきた。

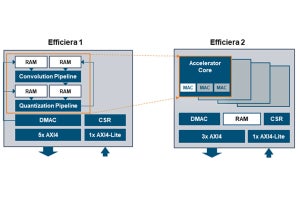

AIアクセラレータを実環境で評価するには、AIアクセラレータと標準システム回路を有するSoC(AIチップ)を開発し、それを用いてシステムレベルでの評価が必要なため、多くのコストと時間が必要となってくる。

そこで、今回の評価プラットフォームでは、共通基盤技術として標準システム回路や検証回路、テスト回路、評価ボードなどを開発し、中小・ベンチャー企業などにこれら共通技術をAIアクセラレータ向け評価プラットフォームとして提供することで、各企業独自のAIアクセラレータ搭載チップの開発とそれを用いたシステムレベルでの評価を短期間に実現することを目指してきたという。

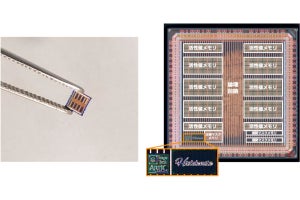

今回の取り組みでは、同評価プラットフォームの実証に向けて、中小・ベンチャー企業が開発した6種類の独自AIアクセラレータを搭載したCMOS 28nプロセスを用いて製造された実証チップ「AI-One」が設計され、評価ボードに実装し、各チップの評価が行われた。現在、各協力会社で自身のAIアクセラレータの評価が進められており、これまでに6種類すべてが設計通りの周波数で動作することが確認されたという。

また、AI-Oneの評価として、SoCの動作確認として一般に行われている方法と同様に、今回の評価用に準備された専用の評価ボードにAI-Oneを実装し、中小・ベンチャー各社のAIアクセラレータの性能確認前に必要な、SoCの基本動作評価として、アクセラレータからLPDDR4メモリへのデータ転送の際のバンド幅、CPUからLPDDR4メモリへの安定した読み書き動作、設計時に各種検証項目で確認した機能や性能の設計通りの動作といったことが確認されたともしている。

今後、協力会社各社が今回、試作された実証チップAI-Oneを用いて、設計段階で見積もった各AIアクセラレータの消費電力や性能などについての比較評価を行い、さらなる評価が進められていく予定。研究チームでは、それらの評価からのフィードバックを活用し、より使いやすいエッジ向けAIチップ評価プラットフォームの確立を目指す計画としている。

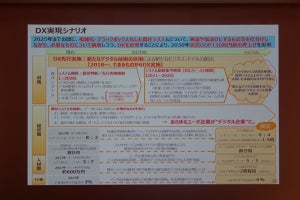

こうした評価プラットフォームの確立により、AIアクセラレータ以外の部品などが共通部分として提供可能となり、チップ全体の設計や時間が短縮できるようになるため、AIチップを短期間(従来比45%以下)かつ低コストに開発することが可能になるという。

また同AIチップ設計拠点では、AIチップ設計に関する共通基盤技術などの開発を進め、さらに使いやすいAIチップ設計環境を構築していくとのことで、これらの取り組みにより、AIチップ設計拠点の確立と、日本の中小・ベンチャー企業などのAIチップ開発を後押しするとしている。

なお、今回開発されたAI-Oneの実チップと評価ボードの展示、AIアクセラレータの評価結果、そしてAIチップ設計拠点については、3月25日に開催される第33回AIチップ設計拠点フォーラムにおいて、詳細が紹介される予定だという。