東京工業大学(東工大)は1月31日、溶液の塗布法を用いた高性能pチャンネル薄膜トランジスタ(TFT)の開発に成功したと発表した。

同成果は、東工大 元素戦略研究センターのキム・ジョンファン助教、細野秀雄栄誉教授らの研究チームによるもの。詳細は、材料科学、物理と化学、医学と生命科学、および工学の基礎から応用までを扱う学際的なオープンアクセスジャーナル「Advanced Science」に掲載された。

論理回路を構成する素子であるCMOSは、nチャンネルおよびpチャンネルのトランジスタを組み合わせることで作られるが、その材料などにより性能が異なってくる。 ディスプレイなどに用いられるTFTの転換点となったのは、2004年の細野栄誉教授らによるインジウム・ガリウム・亜鉛のアモルファス酸化物InGaZnO(IGZO)を用いたTFTの開発。ただし、IGZO-TFTはn型半導体であり、p型半導体については、新規材料の探索が進められているものの、十分な性能を有する材料の発見には至っていなかった。

そこで研究チームは今回、視点を変え、まったく新しい物質を見出すのではなく、既存の物質同士をうまく組み合わせることで優れた半導体特性を実現することを試みることにしたという。

そこで着目されたのが、「金属ハロゲン化物(ヨウ化物)半導体」。大きいイオン半径を持つヨウ素の存在が、優れたp型半導体特性をもたらすことが過去の研究で示されているほか、これらの半導体の溶液を塗布するだけで薄膜作製が可能であることから、低温かつ安価なプロセスでのTFT作製への応用が期待できるという。

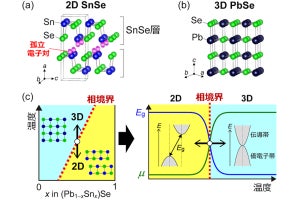

今回の研究では、フェニチルアンモニウムイオン・スズ・ヨウ素からなる2次元構造化合物で良好なキャリア制御性を有するが電気抵抗が高いためにキャリア移動度が低い「PEA2SnI4」と、ホルムアミジウムイオン・スズ・ヨウ素からなる3次元構造化合物で高いキャリア移動度を持つが、キャリア濃度の制御が難しく、常に電流オンの状態になってしまう「FASnI3」の2種類の物質を混在させて微細構造を制御することで、それぞれの長所を生かしつつ、短所を補い合うことができるのではないかと考察したという。

-

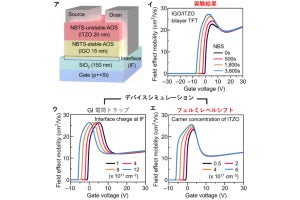

(ア、イ)2次元および3次元ペロブスカイトTFTが抱えている現状の問題点。(ウ)提案される2・3次元コア-シェル型複合相からなるTFT。(エ)2・3次元相の混合層からなるTFT (出所:東工大プレスリリースPDF)

材料設計のコンセプトとして、キャリアが3次元相と2次元相の両方を通過して電流が流れる構造(コア-シェル構造)を作ることが必要であるという仮説を立て、2つの物質の比率、添加物の有無や量などを踏まえたさまざまな薄膜を作製したところ、2次元相(PEA2SnI4)と3次元相(FASnI3)を1:6の比で混ぜた溶液に、微量(2mol%)のフッ化スズ(SnF2)を添加することで、コア-シェル構造が得られることが判明。得られたTFT特性からはコア-シェル構造の優位性が明確であり、約5V付近のしきい値電圧でスイッチングしていることが確認されたとする。

また、2次元相(PEA2SnI4)と3次元相(FASnI3)の比を1:9にすることで、25cm2/Vsという高い電界効果移動度が得られることも確認。この値は従来のIGZO-TFTと同等であり、作製されたCMOSインバータからは、約180V/V(VDD=20V)の高いゲインが得られたという。

なお、研究チームでは実用化に向けては、ペロブスカイト型ハロゲン化物特有の大気中での安定性問題が残っており、その課題解決のためにも、迅速な産学連携が必要だと考えられるとしている。