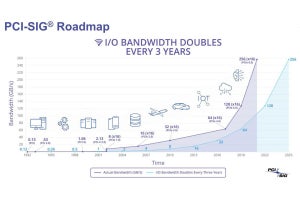

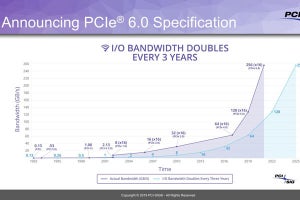

米PCI-SIGは米国時間の1月11日、PCI Express 6.0 Specification 1.0がリリースされたことをアナウンスした。

もともとは2021年中に完成予定だったPCI Express 6.0であるが、ちょっと遅れて2022年1月のリリースとなった、とは言えこの程度であれば十分許容範囲内であろう。

PCI Express 6.0の特徴は、

- 信号速度そのものは32GT/secのまま据え置き

- 変調方式をNRZからPAM-4に変更し、なので転送速度は64GT/secに倍増

- エンコード方式は従来と同じ128b/130bを採用

- PAM-4を利用する事に起因したBER(Bit Error Rate)の向上に対応するため、軽量のFECに加えてFLITと呼ばれる新しいPHYレイヤの再送機構を実装

- 新たにL0pと呼ばれる省電力ステートを追加

といったところになる。

このFECやFLITに関しては以前こちらで説明を行っている。

これによって、1レーンあたりで16GB/sec、NVMe SSD向けのx4なら64GB/sec、アクセラレータ/GPU向けのx16レーンでは128GB/secの転送速度に達する(ちなみにPCI-SIGでは、双方向の通信が可能と言うことで2倍にして256GB/secの帯域と説明しているが、ここに示した数字は片方向のものである)。

すでにRambusは、旧PLDAの提供していたPCIe 6.0対応のコントローラIPをラインナップしているほか、昨年10月にはCadenceがTSMC N5に対応したIPを発表、SynopsysもやはりDesignWave IP for PCIe 6.0をリリースするなど、各社PCIe 6.0対応IPの準備に余念がない。

ちなみに今回PCI-SIGがリリースしたのはBase Specificationだけであり、Test SpecificationやCompliance Specificationのリリースはまだである。FAQによれば、Compliance SpecificationのPreliminary版に基づいての相互接続性テストの実施は2023年度を予定している。また実際に製品が投入される時期に関しては、「一般論として」Specificationのリリースから12~18か月を要するとしており、2023年末~2024年ごろの製品投入を示唆している。