東北大学は12月14日、STT-MRAMの情報記憶素子として、高速書き込み動作を特徴付ける時定数を制御できる磁気トンネル接合(MTJ)構造を提案し、5nm以下の直径を有するMTJ素子で3.5nsまでの高速書き込み動作を実証したと発表した。

同成果は、東北大 材料科学高等研究所の陣内佛霖助教、東北大 電気通信研究所の五十嵐純太学術研究員、同・深見俊輔教授、同・大野英男教授(現・東北大総長)らの研究チームによるもの。詳細は、IEEE主催の半導体のデバイス技術とプロセス技術に関する世界最大級の国際学会「IEDM(International Electron Devices Meeting)」にて発表された。

次世代メモリとして、スピン移行トルク磁気抵抗メモリ(STT-MRAM)の研究開発が進められており、2021年段階では22/28nmプロセスでの量産が行われ、14/16nmプロセスでの実現に向けた技術開発も進められている。そんなSTT-MRAMの情報記憶を担い、性能を決めるのがMTJ素子であり、プロセスの微細化とともに、それ自体の微細化も求められるようになっている。例えば、2021年時点の最先端量産プロセスとなる5nm世代、およびその先にあるオングストローム世代の半導体製造技術では、現在の30nm以上の直径から、10nm以下へと微細化することが必要とされている。

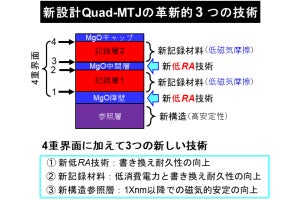

現在の多くのMTJ素子は、2010年に現・東北大総長の大野教授が率いる研究チームによって開発された、CoFeB/MgO界面の垂直磁気異方性を利用したMTJ素子技術がベースとなっているが、この構造では、MTJ素子の微細化に伴ってデータ保持特性の維持ができないため、直径10nmを下回る極微細領域でのMTJ素子開発は困難であったという。

そこで同研究チームは2018年、情報記憶層のCoFeBの膜厚を直径よりも十分に厚くすることで有効に働く、「形状磁気異方性」を利用した「形状磁気異方性MTJ素子」を提案。2020年に、直径10nm以下の極微細領域で車載応用にも適用可能な、十分に高いデータ保持特性ならびに10nsまでの高速書き込みの実証に成功していた。しかし、こうした膜厚が厚い形状磁気異方性MTJ素子では、ラストレベルキャッシュ用SRAMに匹敵する、10nsよりも高速な数nsでのデータ書き込みを実現させるという課題の解決には至っていなかった。

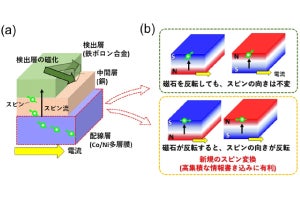

-

MTJ素子は、用途によってデータ書き込み・保持特性の仕様が決まる。同時に、シリコン半導体素子と集積化されるため、MTJ素子の微細化も必須となっている。直径1桁nm(5nm以下)のMTJ素子技術については、研究チームにより、車載応用に適用可能な高データ保持性能を有する素子の動作が実証されている。今回の研究では、SRAM置き換えを視野に入れた、高速動作が可能な直径5nm以下のMTJ素子が開発された (出所:東北大プレスリリースPDF)

今回、研究チームは、高速動作を重視した素子構造にすることで、直径5nm以下のMTJ素子で10ns以下の高速動作を実現したという。今回開発されたMTJ素子の特徴は、2020年に提案された形状磁気異方性MTJ素子と補完する関係となっており、用途に応じてそれぞれのMTJ素子を使い分けることが可能だとしている。

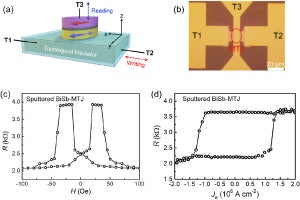

具体的には、MTJ素子のCoFeB層の膜厚を薄くしながら磁気異方性を大きくすることを目的に、CoFeB/MgO界面の数を増やし界面磁気異方性の寄与を大きくしながら、CoFeB層の膜厚を薄くした積層磁性体構造を開発。実際にMTJ素子を作製し、直径2.0nm(20Å)までの極微細MTJ素子の動作を確認したとするほか、MTJ構造を変化させることで、直径5nm以下のMTJ素子で歳差領域の反転電圧増大を抑制しながら、10ns以下の高速書き込みを実現できることを確認したとする。

-

今回作製された積層磁性層構造を有するMTJの透過型電子顕微鏡(TEM)像とその膜構造。CoFeB/MgO層を複数回(画像では4回)積層することで、界面磁気異方性の増大が実現した (出所:東北大プレスリリースPDF)

なお、研究チームによると今回の成果は、STT-MRAMが将来のオングストローム世代の半導体製造技術においても、SRAMや比較的高速なDRAMの代替としても使えることを示すものだとしている。また、半導体デバイスメーカーの既存設備でもこれらのMTJ構造の製造が可能だとしており、今後の技術開発が加速されることが期待されるとしている。