imecは、2025年の高NA(開口数) EUVリソグラフィによる量産適用に向けた現状の課題などに関する情報を公開した。

それによると、高NA(=0.55)のEUVリソグラフィは2023年にASMLより最初のプロトタイプ(EXE:5000)が提供される見通しで、2nmプロセス以降の微細ロジックの生産に適用される見込みだという。NAの向上手法としては、ArF(波長193nm)の時代は、レンズとウェハの間に水を挟むこと(液浸)が行われたが、EUVでは光学系の再設計により高めることで対応するという。NAが従来の0.33から0.55へと向上することにより、1回の露光で16nmピッチのL/S(ライン&スペース)に対応する8nmの解像度を実現できるようになるという。

こうした技術開発はimecとASMLが協業しているHigh-NA Labによるもので、共同で新たなマスク、計測技術、レジスト除去技術、薄膜パターニング用材料開発などといったエコシステムの構築も進めているという。

プロセス微細化で求められるレジストの薄膜化

16nmピッチのL/Sを目指しつつ、2:1の理想的なアスペクト比(ラインの高さと幅の比率)を維持するためには、レジスト膜を20nmよりも薄くする必要がある。レジスト膜が厚くなると、アスペクト比が増加し、ラインが崩壊する危険性があるためである。また、焦点深度(DOF)はレイリーの方程式に従い、NAの2乗で減少するため、シミュレーションからは現在のNA=0.33のEUVリソに対し、2~3倍のDOFの減少が予想されており、薄くする必要があるという。

imecでは、高NA EUCプロセスでは、新たなレジスト除去、ハードマスクとエッチングプロセスの選択制の最適化、極薄レジスト移行時のパターニング限界の評価などを材料サプライヤと協力して研究開発を進めているとするほか、よりそうした極薄レジストになると、従来の計測ツールを使えない場合も生じるため、パターン化の実現と計測手法の確立の両方を同時に進める必要があるともしている。

こうした状況を踏まえ、imecでは現在の先端EUV露光装置となる「NXE:3400B」(NA=0.33)を用いて、L/Sのパターン化における重要パラメータの1つである線端および線幅の粗さ(LER/LWR)が、極薄の化学増幅型レジスト(CAR)の場合、増加する傾向にあることを確認。CARを超える優れた分解能を備えたレジストの探索として、金属酸化物レジスト(MOR)などの新材料の評価などを進めているとする。

一方の新たな計測ソリューションとしては2種類を検討しているとする。1つ目は、従来のCD-SEMのパラメータを微調整することで、画像コントラストの低下に対処する手法で、スキャンレートなどのパラメータを操作することで、15nmまでの膜厚でパターンを確認できるようにしたという。2つ目は、計測サプライヤと協力して代替手法を探索していくというもので、分解能として有望な手法として低電圧SEMやヘリウムイオン顕微鏡、スキャトロメトリなどが考えられているという。

高NA EUVに対応するマスクをどうやって実現するか

半導体製造に不可欠なコンポーネントである「フォトマスク」も、プロセスの微細化に伴う課題を解決することが求められるようになっている。

現在のEUVマスクは、シリコン(Si)とモリブデン(Mo)が交互に40〜50層ほど形成され、それを薄いルテニウム(Ru)層で覆われた、厚さ約300nmの反射多層スタックで構成されている。このスタックには、硝酸タンタル-硝酸ホウ素(TaBN)で作られた吸収体でパターンが形成されている(MoとSiの多層が入射光を反射する一方で、吸収体で反射をブロックする)。

現在のTaベースの吸収体は、一般的に約60〜70nmの厚さで、十分な量の光を吸収するように設計されているが、この厚みはEUV光(13.5nm)に対し大きく、マスク3D効果(マスクトポグラフィ効果)が生じ、寸法精度に影響を与えることから、高NA DOFの向上に役立つパラメータとして、マスク材料の改善が求められているという。

新たなマスク構成材としては、異なるEUV屈折率(low-n材料)や高いEUV吸光係数(PtTeや高い吸収能力を持つNi)を持つ材料が考えられ、imecとしても、有望な材料の精査を進めており、2021年末までに実際にEUV露光を新たなマスクアーキテクチャを用いて実施する計画だとしている。

また、高NA EUVリソでは、入射角が大きい光がウェハにあたるようになるが、そのままでは3Dマスク効果を悪化させることとなる。こうした影響を解決するアプローチの1つとして、より大きなマスクブランクを使用することと併せて、マスクの倍率を従来の4倍から8倍に高めることが考えられているが、そのままではこれまでの6インチレチクルが使えなくなるデメリットが生じる。

この解決策として、ASMLとZeissは、結像されるイメージの縮小率が縦・横方向で異なるアナモルフィクレンズを導入。具体的には、x方向に4倍、y方向に8倍とすることで6インチのマスクサイズを維持した。しかし、これではデザインが一方向に引き伸ばされることとなるため、1ステップで露光されるウェハ部分(フィールドサイズ)は半分となり、特にダイサイズが大きいチップの場合はその一部のみパターンが形成されるため、設計方法に制約が課せられることとなる。この場合、チップメーカーは、2つのマスクを別々に使って露光し、それを縫い合わせるステッチングと呼ばれる手法を用いる必要が生じることとなる。そのためimecでは、2つのマスク間に本質的に存在する遷移ゾーンを減らすことで、ステッチの改善に向けた研究開発を進めているとしている。

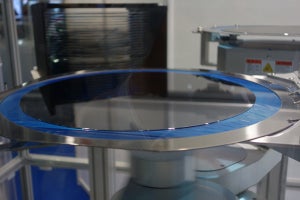

さらに露光工程においてフォトマスクは通常、パーティクル汚染からマスクを保護するためにフォトマスク表面から数mm上にペリクル膜を取り付け保護されることとなるが、高NA EUVでは、やはりペリクルによる光の吸収をできるだけ少なくし、スループットも確保する必要もあり、かつさらなる将来の露光装置にて増加するであろうEUV光の出力に耐えることが求められる。そのためimecでは、パートナーと協力し、600Wを超すEUV光の出力に耐える可能性のあるCNT(カーボンナノチューブ)ベースのペリクルを開発したという。すでにASMLのNXE:3300にて試験され、その有用性が実証されているとしており、現在imecでは、高NAを含む次世代EUVリソツールに適した高生産性ペリクルの実用化を目指した取り組みを進めているとする。

高NAパターニングエコシステム開発を加速するAttoLab

このほか、imecと特殊レーザーメーカー米KMLabsとの共同研究施設「AttoLab」では、ASMLのEXE:5000プロトタイプが利用可能になる前ながら、高NA EUVリソ条件下でのフォトレジストイメージングの基本的な調査が進められている。

最近の研究では13.5nmの高NA露光を、明るくコヒーレントな高次高調波EUV光源でエミュレートすることで、20nmピッチのL/Sを金属酸化物レジストを用いて正常にパターニングできることが確認されたという。

ここで用いられている手法はスループットに問題があり半導体の量産に向かないが、imecでは、これを活用することで、レジスト材の研究を進め、課題の洗い出しなどを進めているという。