東芝は10月29日、GaNやSiCなどの次世代パワー半導体の制御を1チップで実現するドライバICを開発したことを発表した。

同技術の詳細は2021年10月10日から14日までオンラインで開催されたIEEEの国際学会「ECCE2021(2021 IEEE Energy Conversion Congress and Exposition)」で発表された。

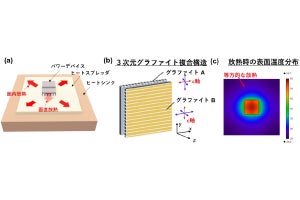

シリコンパワー半導体を超える性能を実現できる次世代パワー半導体の活用に期待が高まっているが、従来同様の回路方式で制御した場合、電力損失の低減と引き換えにノイズが発生しやすくなるほか、放熱経路が小さくなるため、短絡などの事故が発生した場合の温度上昇により、半導体が壊れる可能性が高くなる、といった課題がある。こうした課題の解決に向け、追加部品としてフィルタや放熱部品が必要となるが、その場合、電力変換器というシステムとして見た場合、小型化が進まず、効率についても低効率となってしまうという問題があるという。

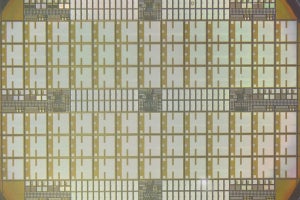

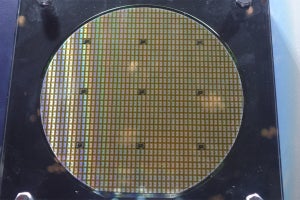

今回の研究は、そうした課題を1チップで解決できるドライバICの実現を目指して進められたもの。具体的には、CMOSプロセスをベースに、「分解能向上」技術ならびに「アナログ波形前処理」技術を新たに開発搭載することで、こうした問題の解決のめどが立ったとする。

分解能向上技術はきめ細かな制御を可能とする技術。低速なデジタル回路と高速なアナログ回路を組みあわせ、パワー半導体に送る信号を特徴的な部分だけを制御することで実現したとする。一方のアナログ波形前処理技術は、パワー半導体の高速な電圧・電流波形をすべて取得するのではなく、制御や事故の検知に必要な特徴量だけを抽出する前処理回路を考案。低速なA/Dコンバータのみで、マイコンなどを経由することなく故障検知を可能とし、即座にパワー半導体を保護することを可能にしたという。

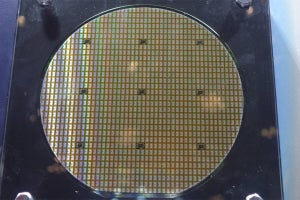

実際に、1.2kV 31AのSiC MOSFETパワー半導体と0.5μmで製造した1チップドライバICを用いて実証実験を行ったところ、従来方式の制御手法に比べ、電力損失を増加させることなく、ノイズ発生の主要因の1つであるサージ電圧を51%低減できることを確認したほか、事故波形もマイコンを介さないため2μsで検知できることを確認したとする。また、インバータを構成した場合、同技術を用いると、従来方式比で電力損失を25%低減できることも理論計算から判明したとする。

なお、同社では今後、製品のさらなる作りこみや、シリコンパワー半導体との組み合わせ評価、信頼性の評価などをさまざまなシステムにて行っていき、2025年の実用化を目指すとしている。