Marvellは、TSMCの3nmプロセスに独自IPコアを搭載したクラウドデータセンター、5G、自動車ならびにエンタープライズ市場向けASICの開発を進めていることを明らかにした。

また、このASICはTSMCのCoWoS(Chip on Wafer on Substrate)を活用したマルチチッププラットフォームとする予定で、これによりユーザーは要求の厳しいクラウドデータセンターアプリケーション向けなど先端システム向けの高性能プロセッサASICを構築できるようになるという。

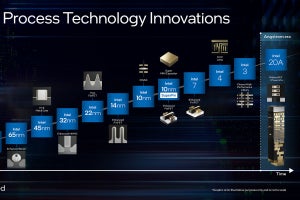

TSMCの先端プロセスロードマップでは、3nmプロセス(N3)のリスク生産を2021年中に開始し、2022年に大量生産を開始する計画である。Marvellでは、このスケジュールに併せる形で複数のユーザーと

TSMCは、予定通り、3nmプロセス「N3」でのリスク生産を2021年中に始め、2022年には量産を開始すると、先日明らかにした。このスケジュールに合わせて、Marvellはすでに複数のデータインフラストラクチャイノベータと協力してユーザー独自のマルチチップASIC構成に向けた協業を進めているという。

Marvellのほかにも、TSMCのN3を活用した半導体チップの製造についてはAppleやIntelなども進めていくことを計画しており、TSMCも「すでにN3の製造委託予約がいくつも入っており、初年度のN3の新規テープアウトがN5(5nm)の時よりも多くなることを期待している」と述べている。

こうした動きは半導体メーカー(Apple含む)のみならず、Googleが自社スマートフォンPixel 6/6 Proに、独自開発プロセッサ「Google Tensor」を採用するなど、最終製品の差別化要因として自社開発の半導体を活用する動きが広がっている。例えば、Alibaba子会社のAlibaba Cloudは10月19日付で、データセンタサーバ向け5nmプロセッサ「Yitian 710」を開発したと発表している。

中国では、5nmデバイスは技術的に製造できないはずだが、どこが製造したかのかについては明らかにされていない。台湾半導体業界関係者の間はTSMCが製造した可能性が高いと見ており、今後も中国勢による先端プロセスを活用したデバイスが登場してくることが見込まれる。その一方で、中国内での半導体製造を強化する動きもあるが、米国政府の輸出規制などがあり、10nm以下の微細プロセスが果たして実現できるのかどうかが注目される。