シリコンカーバイド(SiC)パワー半導体メーカーのUnitedSiCは9月14日、ドレイン・ソース間オン抵抗(RDS(on))の値を6mΩまで抑え、電力の損失を低減させることができる750V SiC FETを発表した。

この6mΩデバイスは、競合する製品に比べてRDS(on)値が半分以下に抑えつつ、 短絡耐量5μsを実現したという。

また、同社では、すでに発売されている18mΩおよび60mΩのデバイスと今回の6mΩデバイスに加え、9/11/23/33/44mΩのデバイスをTO-247-4Lパッケージで新たに提供するとしているほか、23/33/44mΩのデバイスについてはTO-247-3Lでも提供するとしている。

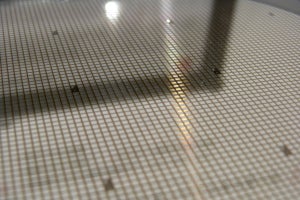

同社は2020年4月に定格電圧を上昇させつつ、高度なセル密度を実現し、単位面積あたりのRDS(on)を低減させる、第4世代(Gen4)に位置づけられるSiC FET技術を発表し、同年12月にこの技術を採用した750Vの18mΩならびに60mΩデバイスを発表していた。

Gen4テクノロジーを採用した製品は、同一のフットプリントまたはパッケージにて、使用温度範囲全体で最小の導通損失や、ハードスイッチングアプリケーションに関しては、RDS(on)×Eoss(Electrical Over Stress Score:過電圧・過電流ストレス値)でみるFoM(Figure of Merit)は競合他社の約2分の1と優れているとしている。

ソフトスイッチングアプリケーションにおいても、高い電力密度を維持し、ゲートドライブ損失が競合製品と比べ、5分の1~10分の1であるとしている。

適応用途は、低いRDS(on)を活かし、EVのトラクションインバータ、ワイヤレスチャージャー、データセンターなどが考えられるとしている。

また、設計に際し、さまざまなアプリケーションで、UnitedSiCのすべてのFETとダイオードを評価可能な「Jet Calculator 2.0」を用意しており、無料かつ登録不要で利用することが可能だという。

なお、今回発表された750V Gen4 SiC FETは、同社の正規代理店からすでに購入することが可能な状態となっている。