産業技術総合研究所(産総研)は8月5日、シリコンスピン量子ビット素子を用いた大規模集積量子コンピュータの実現に向けて、スピン量子ビット素子と演算に必要な微小磁石を集積した新しい集積構造を考案したことを発表した。

同成果は、産総研 デバイス技術研究部門 新原理デバイス研究グループの飯塚将太産総研特別研究員、森貴洋主任研究員らの研究チームによるもの。詳細は、2021年6月13~19日にオンライン開催された国際会議「2021 Symposia on VLSI Technology and Circuits」において発表され、ハイライトペーパーに選ばれた。

プロセスの微細化、いわゆるムーアの法則に沿ったコンピュータの高性能化は物理的限界を迎えつつあるが、コンピュータに求められる性能向上は未だ止まることを知らない。そのため、ムーアの法則のその先を実現できるコンピュータの実現が求められており、その1つとして量子コンピュータの実用化が期待されている。

しかし、本格的な量子コンピュータの実用化には、100万個を越すスピン量子ビットを集積する必要があるとされ、まだまだその道のりは遠く、実現のためのさまざまな技術課題がある。

産総研は、高温動作が可能なスピン量子ビットや量子ビット制御回路などの開発で、微細シリコン量子コンピュータハードウエアの実現に向けたデバイス技術・集積化技術に関する研究を進めてきており、今回の研究も、スピン量子ビット素子の高速動作に必要な微小磁石を集積する新しい構造についてのものだという。

今回提案された構造では、従来スピン量子ビット素子の上部にあった微小磁石を、素子の側方下部に形成するという点が特徴。微小磁石がスピン量子ビット素子により近づくので、高速操作に適したより強い傾斜磁場を得ることが可能となるのと同時に、上部に配線スペースを確保できるので、自己整合型プロセス技術と呼ばれる製造ばらつき耐性を高める製造方法を採用することができる点がポイントとなっているという。

提案された構造では、まず汎用量子コンピュータの実現に必要とされる格子状のビット配置が想定され、シミュレータの計算結果からは、上面から見たときに、スピン量子ビット素子の四隅のうち2か所に微小磁石を配置した場合が、最も強い傾斜磁場強度を得られることが確認されたという。

また、提案された構造について製造ばらつき耐性の検証の結果、自己整合型プロセス技術を採用することで、量子ビットそのものが位置基準となるので、スピン量子ビット素子と微小磁石との相対ずれがなくなり、製造ばらつき耐性が高く、特性不良が発生しにくくなることが示されたとする。

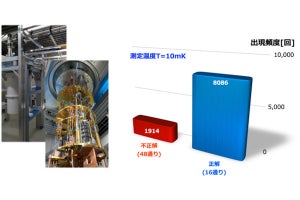

このメリットを、スピン量子ビット素子の最も重要な性能パラメーターである演算エラー発生率を用いて検証したところ、今回の構造を採用することで4nmでも演算エラー発生率を1%以下に保つことができることが示されたという。

研究チームは今後、産総研の開発したスピン量子ビット素子特性を模擬できるデバイスシミュレーション技術を活かし、大規模集積が可能な量子コンピュータ技術の設計や検証を引き続き進めていくとしているほか、量子コンピュータの実現に必要となる演算の実行、演算結果の読み出し、スピン量子ビット素子の結合などの要素を含めた量子回路の設計も行うとしている。