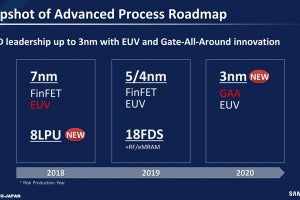

7月上旬に中国で開催された半導体エコシステム関連イベントで、韓Samsung Electronicsがロジックファウンドリの最新技術ロードマップを公開したと、参加した中国人が撮影したものと思われるSamsungのスライドとともにBaidu(百度)などのSNSで報告しており、業界内で話題になっている。

それによると、

- 2020年:5LPE(5nm FinFETプロセスの初期版、LPはLow Powerの略、EはEarlyの略で初期版を意味する)

- 2021年:5LPP(5nm FinFETプロセスの改良版:最後のPはPlusの略で改良版を意味する)

- 同上:4LPE(4nm FinFETプロセスの初期版)

- 2022年:4LPP(4nm FinFETプロセスの改良版)

- 2023年:3GAP(3nm Gate-All-Aroundプロセスの改良版、GAはGate-All-Aroundの略、PはPlusを意味する)

と書かれているという。

Samsungが以前発表したロードマップと比べると、

- 2021年:5LPP

- 2022年:4LPP

が追加となり、逆に、

- 2022年 3GAE

が消えている模様だ。

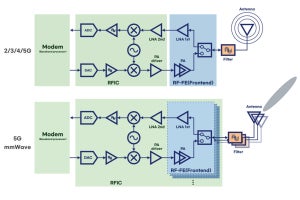

3nm Gate-All Around(GAA)の初期版である3GAEは、従来プロセスや構造とはギャップが大きいため、立ち上げに時間がかかると見られており、どうやら最新の判断ではSamsung社内だけで少量生産を進めることにし、ファウンドリでは扱わなくなったのではないかとの見方が業界関係者からでている。ちなみに、5nm以降の微細プロセスではFinFETであろうとGAAであろうと、EUVリソグラフィを多用することになっている。

TSMCは3nmでもFinFETを活用

Samsungが3nmでGAAを採用するのに対し、競合ファウンドリで業界最大手のTSMCでは、3nmでも従来同様FinFETプロセスを用いる予定で、それにより2021年内のリスク生産開始、2020年後半からの量産開始を計画している。Samsungは2019年に3nmでGAAを採用することを発表したが、これはナノシートを採用した垂直多段積層Gate-All-Aroundであり、独自の名称であるMulti-Bridge-Channel FET(MBCFET)と同社では呼んでいる。

Samsungがナノワイヤの代わりのナノシートを採用するのは、MOSトランジスタのチェネル幅を広げて電流駆動能力を高めるためであり、Samsungだけでは、他社も追随していく見込みである。

当時、Samsungは3GAEのパフォーマンスは、7LPEと比べて35%向上しつつ、消費電力が50%削減し、面積が45%削減すると説明していたほか、3GAEを使用した量産を2021年後半に開始するとしていたが、その後、徐々に時期を後ろ倒しにしている。

最先端となる3nmプロセスの量産競争では、TSMCが従来から実績のあるFinFETを踏襲してSamsungを突き放すか、それとも性能面で有利と見られるGAAをSamsungが無事に立ち上げ、TSMCを追撃できるか、はたまた生産トラブルで後れをとることとなるのか、その動向が注目される。