東芝は6月2日、シリコンパワー半導体として、電力のオンとオフが切り替わるスイッチング時の電力損失(スイッチング損失)を全体で最大40.5%低減できるトリプルゲートIGBTを開発したことを発表した。

同成果の詳細は、2021年5月30日から6月3日にかけて オンラインで開催されているパワー半導体の国際学会「I SPSD2021」にて発表された。

IGBTで発生する電力損失はスイッチング損失と導通損失で計算されるが、スイッチング損失はキャリア(電子とホール)の注入と消滅の速度に依存するため、電子とホールを高速に注入、消滅することで低減できる。そのため、ゲート電極を2つ有するダブルゲート方式のIGBTの開発が進められてきた。今回の研究では、さらなる損失の低減を目指し、ゲート電極を3つ有するトリプルゲート方式と適切なゲート制御技術を考案、従来のシリコンIGBTの性能限界を超えることが可能であることを確認したという。

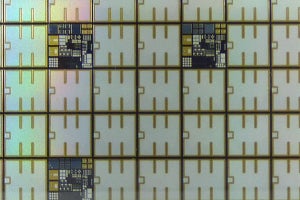

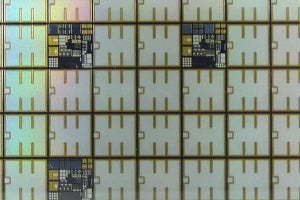

具体的には、1チップ上にそれぞれ独立に駆動するメインゲート(MG)、第1コントロールゲート(CGp)、第2コントロールゲート(CGs)の3つのゲートを設計。ターンオン時はMGならびにCGpに対してCGsを遅延させるようにゲートを制御すると、MG・CGp・CGsの3つのゲート電極が同時にオンとなり、その結果、IGBT内に大量の電子とホールが高速に注入、蓄積されることで、 スイッチング時間が高速化し、ターンオン損失を低減できるようになったという。

一方のターンオフ時は、CGsはオフ状態としておき、MGに対してCGpを先にオフさせることで素子内部の電子とホールを減少させ、これによりMGのオフするタイミング(=IGBTが完全にターンオフする時)で電子とホールが高速に消滅し、ターンオフ損失を低減できるようになったという。

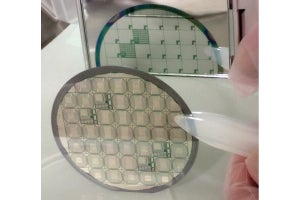

実際に試作したトリプルゲートIGBTを動作させると、シングルゲートIGBTと比べて、ターンオン時、ターンオフ時ともに、高速に動作していることが確認されたという。

ターンオン損失は最大で50%の低減、ターンオフ時は最大28%の低減が確認され、全体のスイッチング損失としては最大40.5%の低減を図ることができることが示されたという。

同社によると、今回のトリプルゲート方式を他社に先駆けて実現できたのは、長年にわたるダブルゲート方式の開発による性能向上やデバイス特性に対する理解が進んでいたためとしている。

今後は、実用化に向けて2-3年をかけて信頼性を中心とする課題の解決を図っていき、実用化を目指すとしている。ただし、既存のIGBTと比べてゲートが増えるため同じパッケージでピンコンパチで差し替えて使う、といったことは難しいとの見通しを示しており、中継基板を活用する形で従来基板を置き換えずに代替できる技術の開発なども行っていきたいとしている。