Applied Materials(AMAT)は5月5日(米国時間)、DRAMのさらなるスケーリングとチップのPPACt(性能、消費電力、面積あたりコスト、市場投入までの期間)改善を加速する3つのマテリアルズ・エンジニアリング・ソリューションを発表した。

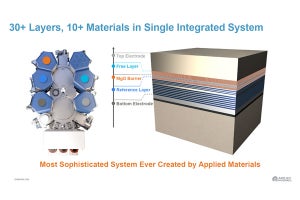

各ソリューションはDRAMのストレージキャパシタ、インターコネクト配線、ロジックトランジスタの3つの分野に焦点を置いて開発されたもので、現在、量産立ち上げ段階にあるという。

1つ目のストレージキャパシタ向け材料は、キャパシタ孔の径を狭めながらも、孔の長さを伸ばして表面積の最大化を図る際に用いられるハードマスクの課題を解決するためのハードマスク材料「Draco」。同社のエッチング装置「Sym3 Y」と合わせて使えるよう協調最適化されており、このプロセスをAMATの電子ビーム測定・検査装置「PROVision」でモニターすることで、毎時50万回近い計測を行うことが可能になるという。

また、Dracoを用いたハードマスクはエッチング選択性を30%以上高めることができるため、マスクの膜厚をより薄くすることが可能であり、これにより、よりまっすぐで均一な正円柱形のパターン孔の形成を可能にするとしている。

2つ目のインターコネクト配線向け材料としては、メモリアレイと信号をやり取りする配線の絶縁材料としてこれまで使われてきたシランもしくはテトラエトキシシラン(TEOS)といったシリコン酸化物が、配線層間膜が薄くなりすぎて金属線の容量性カップリングを防ぎきれなくなってきたという課題を受けて、新たなLow-k絶縁膜「Black Diamond」が提供される。

同材料は、これまでにも先端ロジックデバイス向けLow-k絶縁材料として活用されてきたもので、これをDRAM市場向けに同社の高生産性プラットフォーム「Producer GT」上で活用してもらうことで、より微細でコンパクトなインターコネクト配線を実現できるようになり、その結果、信号がチップ内を数GHzで行き来しても干渉が起きず、消費電力を低く抑えることができるようになるとしている。

そして3つ目のロジックトランジスタ向け材料としては、こちらも先端ロジックデバイスですでに活用されているHigh-k/メタルゲート(HKMG)トランジスタの採用だとしている。従来のトランジスタはポリシリコン酸化膜ベースで製造されてきたが、プロセスが微細化するとゲート絶縁膜も薄くなり、それに伴い電子のリークが生じやすくなるという課題があった。この課題に対し、すでにロジックデバイスでは、ポリシリコンに代えてメタルゲートとし、かつ絶縁膜に酸化ハフニウムを用いることで性能向上と消費電力の低減、そして面積当たりのコスト低減を実現しており、DRAMにも同様に適用することで、同じメリットを得ることができるようになると同社では説明している。

なお、同社によると、DracoハードマスクとLow-k絶縁膜Black Diamondは主要なDRAMメーカーにすでに採用されており、HKMG DRAMの導入も進められている状況で、今後数年間にこうしたDRAM技術の転換がさらに進むことが期待されるとしている。