米国国防高等研究計画局(DARPA)は3月18日(米国時間)、Intelおよびフロリダ大学、メリーランド大学、テキサスA&M大学らと協力して、国防電子システム向けに10nmプロセスを用いたASICの製造に向けた契約を取り交わしたことを明らかにした。

具体的には、防衛電子システム用の10nmプロセスを採用したカスタムチップの米国内での開発、製造を目的としたプログラム「SAHARA(Structured Array Hardware for Automatically Realized Applications)」として、開発と製造併せて3年間のパートナーシップとしている。

これまで、10nmプロセスのASICを製造できるファウンドリは米国内にはなかったが、Intelがファウンドリサービスの提供を開始することを踏まえ、DARPAは、このパートナーシップにより、安全な軍用電子機器の開発にIntelの最先端のファウンドリ機能を使用できるようになるとしている。

SAHRAの前3文字を意味するStructured Array Hardwareは、FPGAやStructured ASICなどといった回路構成をプログラマブルに変更できるハードウェアを意味する。FPGAはまだしも、Structured ASICは近年、あまり話題になっていないが、すべての顧客に共通に用意されたゲートアレイのプラットフォーム上に最後に顧客ごとに異なったマスクを使って金属配線を形成し顧客の所望する機能を搭載したゲートアレイチップを実現する手法であり、顧客独自のマスクは一切用いず、チップ完成後にプログラムで回路構成を構築するFPGAと、顧客独自のマスクを数十枚駆使して製作するASICの中間に位置する存在として長年、半導体業界で提供されてきたものである。

SAHARAでは、防衛向けFPGAの設計をStructured ASICに人手を経ずに自動的かつスケーラブル変換することを、米国ベースの製造機能で実現しようというもので、参加大学の研究者たちは、データとIP(知的財産)をリバースエンジニアリングや偽造から保護するためのセキュリティ検証や評価などを担当するとしている。

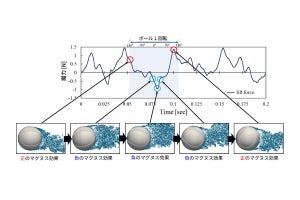

FPGAはすでに現在、多くの軍事用途で使用されているが、Structured ASICは、そのFPGAに比べ高いパフォーマンスと低消費電力を実現できると期待されており、防衛用電子システムで用いられているFPGAの効率的かつ効果的な代替手段となると考えられている。しかし、FPGAをStructured ASICに手動で変換することは、複雑で、時間とコストのかかるプロセスであるため、経済的負担が大きすぎるほか、現在、世の中に出回っている変換プロセスでは、設計のセキュリティに関する考慮事項に対応していないことからSAHARAでは、設計プロセスの短縮と、関連するエンジニアリングコストの削減を図りつつ、チップのセキュリティ強化に向け、Intelの開発チームによるサプライチェーンにおけるセキュリティの脅威に対処するための独自のチップ保護技術を組み入れながら、変換プロセスの自動化に取り組むとしている。

なお、Intelは、2015年にFPGAベンダのAlteraを、2018年にはStructured ASICベンダのeASICをそれぞれ買収し、シームレスにそれらの製品を提供できる体制を構築してきた。

米国防総省の研究およびエンジニアリング担当次官補室(USD R&E)でマイクロエレクトロニクス担当デュプティプリンシパルディレクター(副部長)を務めるBrett Hamilton氏は、「SAHARAで開発されたStructured ASICプラットフォームとその実現方法、およびSHIP(State-of-the-art Heterogeneous Integrated Packaging:DARPAとIntelがすでに締結している先端半導体実装に関するパートナーシップのプロジェクト)で開発された高度なパッケージング技術により、米国防総省は、国防に不可欠な高度な先端マイクロエレクトロニクスシステムをより迅速かつコスト効率よく開発および展開できるようになる」と述べている。

また、DARPAのマイクロシステム担当プログラムマネージャーであるSerge Leef氏は、「SAHARAによってFPGAからStructured ASICへの変換を人手を経ずに自動的に行えるようにすることで、ASIC開発期間の60%短縮、ならびにエンジニアリングコストの1/10への低減、そして消費電力の50%削減を目指す。今回のパートナーシップにより、最終的に国防総省にはコストとリソースの節約というメリットがもたらされると同時に、多数の国防アプリケーションで最先端のマイクロエレクトロニクスを活用できるようになる」と、今回のプログラムの意義を語っている。