フランス原子力・代替エネルギー庁 電子情報技術研究所(CEA-Leti)は、半導体設計会社である仏Dolphin Designと協業し、FD-SOIの動作周波数を450%向上させつつも、消費電力を30%削減させることに成功したことを2月13日~22日にかけてオンラインで開催された「国際固体素子回路会議(ISSCC 2021:International Solid-State Circuits Conference 2021)」にて発表した。

FD-SOIは、バックゲートとして機能するトランジスタ本体のバイアス(ボディバイアス)を可能にする技術で、これによってしきい値電圧を制御することが可能となり、プロセス、電圧、および温度(PVT)の変動を補償することができる。これにより、例えばスイッチ操作では、スイッチがオンのときに、ボディバイアスの印加によりしきい値電圧を下げて、より多くの電流を流すことでオン抵抗を減らすことができるようになる。また、オフ状態では、ボディバイアスによりしきい値電圧を上げることでオフ抵抗を上げ、その結果、リーク電流を減らすことができるようになる。

今回の研究成果について、研究チームは、「一般的によく知られている適応型バックバイアス(Adaptive Back Biasing:ABB)アーキテクチャは、プロセスと温度に応じてVTHの変動を補償することで、消費電力を削減したり、動作周波数を維持することを可能としてきた。しかし、これまでのABBアーキテクチャでは、FD-SOIを半導体の量産向けデジタル設計フローにシームレスに統合することは難しかった。そこで、0.4〜100mm2のバイアスのかかったデジタル負荷を活用することで、そうした既存の課題を克服するIPの開発に成功した」と説明している。

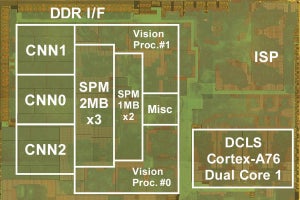

ちなみに論文のタイトルは、「A 0.021 mm2 PVT-Aware Digital-Flow-Compatible Adaptive Back-Biasing Regulator with Scalable Drivers Achieving 450% Frequency Boosting and 30% Power Reduction in 22nm FD-SOI Technology」で、直訳すれば、22nm FD-SOI技術を用いて、動作周波数を450%向上させつつ、消費電力を30%削減する縮小可能なドライバ搭載の専有面積0.021mm2 PVT(プロセス、電圧、および温度変動)対応デジタルフロー互換適応型バックバイアスレギュレータ、といったものとなる。

具体的には、新たなABBアーキテクチャをFD-SOIに適用することにより、ボディバイアス技術を使用しないプロセス技術と比較して、22nm FD-SOIプロセスを用いたプロセッサにおける電力消費を最大30%削減しつつ、動作周波数を最大450%向上させることができたとしている 。また、製造歩留まりの向上も確認したという。

なお、CEA-LetiのFD-SOI研究者で、ISSCC 2021の発表論文の著者であるGaël Pillonnet氏は、「FD-SOIに最適化したABBの開発は、FD-SOIの性能と歩留まりを向上させるのに役立つブレークスルーである」と述べている。