キオクシアとWestern Digitalは、2月13日~22日にかけてオンラインで開催された「国際固体素子回路会議(ISSCC 2021:International Solid-State Circuits Conference 2021)」にて、第6世代となる162層3D NANDフラッシュメモリ技術「BiCS 6」を開発したことを発表した。

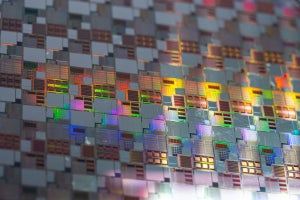

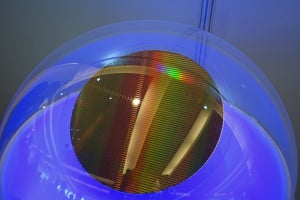

この第6世代3D NANDメモリは、従来の8列配置したメモリホールアレイよりも先進的な構造を採用することで、第5世代技術比で、平面方向のセルアレイ密度を最大10%向上させることに成功。この平面方向のスケーリングの進化と、162層を垂直方向に積層したメモリを組み合わせることで、112層の第5世代と比較してダイサイズを40%削減することができたという。

さらにCircuit Under Array CMOS配置技術と4プレーン動作を採用することで、前世代比で書き込み性能を約2.4倍向上、読み出しレイテンシも同10%の短縮を実現したほか、I/O性能も同66%向上させることに成功したとのことで、次世代インタフェースに準拠できるようになったとしている。

これらの技術を活用することで、ビットあたりのコストを削減しつつ、ウェハあたりの製造ビット数を前世代比で70%増加させることに成功したと両社は説明しており、今後も多様なアプリケーションニーズへ対応することを目指し、持続的なスケーリングを可能とするイノベーションの推進を図っていくとしている。