2月3日~12日にかけてオンライン開催された「SEMICON Korea 2021」では、SK HynixのEVP兼DRAM開発責任者のSeon Yong Cha氏が「DRAMメモリにおける経済的、社会的、環境的持続可能性」と題して基調講演を行った。

同氏の講演は、まず最近のデジタルトランスフォーメーション(DX)の加速から話が始まり、「DX時代を迎えるにつれ、私たちが毎日生成するデータの量は飛躍的に増加した。また、5GとAIの出現により、自律型、ヘルスケア、AR/VRといった新たなアプリケーションで世界がよりスマートなものとなったほか、新型コロナウイルス感染症(COVID-19)の流行が私たちの生活のあらゆる側面に影響を及ぼし、社会、経済、科学、技術における“非接触”サービスの需要を継続的に増加させることで、デジタル変革がさらに加速されている」とDXのプラスの面を紹介した。

一方のマイナス面についても、「同時に、DXがエネルギー消費を促進し、地球上にCO2とPM2.5のような微粒子状物質を排出しており、ESG(環境、社会、企業統治)が業界の重要なトピックの1つとして浮上している」としている。

SKグループでも、会長の指示によりESGを各企業の業績評価指標としているという。Cha氏は、半導体デバイス開発におけるESG対応について「SK Hynixは、半導体デバイスのプロセスを縮小することで製品の消費電力低減を継続的に図ってきたが、物理的な限界に近づくにつれてスケーリング(比例縮小)の速度は遅くなってきている。このような状況に対応するためには、新しいプラットフォームで革新的な製品を開発することが不可欠であり、そうした技術開発を進めている。ただし、1社だけでは社会的・環境的責任を果たせないため、業界の他のステークホルダーと共同で技術協力を行うことも重要である」とし、データセンターで消費される膨大な電力の低減は持続的な地球環境維持のために必須課題であり、そのためにはHDDのSSD化に加えて、ストレージクラスメモリの導入、HBMのHBM3への進化、キャッシュとDRAMのスピード差を埋め消費電力を低減するULM(Ultira Low-power Memory)、AiM(Acceleration in Memory)などさまざまな工夫を取り入れることが必要だとした。

DRAM量産でのEUVリソグラフィ導入が現実に

SEMICON Koreaでも、日本を含む他国のSEMICONと同様に、技術セミナーである「SEMI TECHNOLOGY SYMPOSIUM(STS)」が開催された。

セッションは、「先端リソグラフィ」、「先端材料およびプロセス技術」、「デバイス技術」、「プラズマサイエンスおよびエッチング技術」、「CMPおよび洗浄技術」、「パッケージングおよび相互配線」の6セッション構成となっていた。

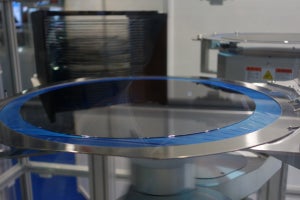

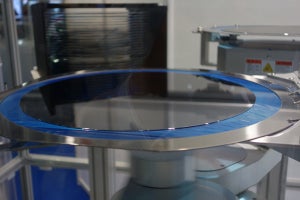

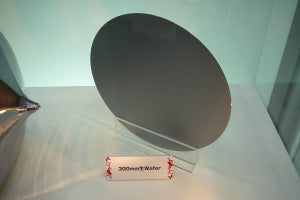

リソグラフィセッションは、EUVリソグラフィの実用化一色という感じで、韓国勢のSK Hynix、Samsung Electronicsに加えて、ベルギーimec、ASML、IBM、米ImpriaがEUVリソグラフィに関する講演を行った。SK Hynixは韓国の本社工場に竣工したばかりのM16ラインで1α-nm DRAMを2021年後半にEUVリソグラフィを用いて生産する予定だが、同社はSTSでDRAMへのEUV導入に関する講演を行った。

それによると、DRAMのViaホールにEUVを導入すると総ウェハコストを20%低減でき、配線層への導入でさらに3.2%低減できるという見通しが示された。

また、EUVリソの生産性改善のためには、新材料を使用した位相シフトマスクの使用が有効との見解も示したほか、透過率88%のぺリクル膜を装着することでスループットが25%低下、同82%のペリクルでは同35%の低下となるため、透過率の高いぺリクル膜が実用化するまではDRAM製造では露光時間が長くなってしまいスループットが低下するためぺリクル膜を使わない方針であることを明らかにした。ロジックデバイスと異なり、DRAMは冗長回路によって不良ビットの救済ができるため、ロジックほど欠陥低減の要求は厳しくなく、ぺリクルを使わなくてもよさそうだという。

このほか、SamsungのEUVプロセスを用いて先端プロセッサを製造委託しているIBMは、3nm以降のプロセスでは高NA(NA=0.55)EUV露光装置が必要となり、高NA露光装置の単純露光の方が従来のEUVL露光装置の2重露光よりも低コストになるという見解を示した。この件についてはimecがすでに同様な見解を明らかにしている。IBMは高NA露光装置の導入により、確率的なフォトン量とレジスト成分の揺らぎによるパターン欠陥の発生を抑制でき、重ね合わせ精度の要求も緩和できるので、高NA EUV露光装置の実用化を期待していると述べた。

ASMLは、客先ですでに7/5nm以降のロジックに加えて16nm以降のDRAMでもEUVが適用されている事例を紹介したほか、リソグラフィのロードマップに沿って引き続き高NA(NA=0.55)のEUV露光装置を開発中であるとした。

なお、洗浄セッションでは、東京エレクトロンが、高アスペクト比の回路パターン倒壊防止のため、究極的には表面張力の発生しない超臨界洗浄乾燥が必要で、高アスペクト比のキャパシタ構造を有するDRAMに続いて、垂直積層ゲートオールアラウンド構造のロジックデバイスや高層の3D NANDフラッシュメモリでもいずれ採用せざるを得なくなるとの予想を発表している。