ASICやSoCを開発する必要のある企業向けシリコン設計サービスプロバイダである台Alchip Technologiesが、TSMCの最先端5nm EUVラインで製造することを前提とした5nm商用ASIC設計の受託サービスを開始したと発表した。

同社は、TSMCの5nm EUVプロセスに準拠した最初のASIC設計受託・支援会社となったという。最初の5nmテストチップテープアウトは2020年12月に予定されている。なお、同社はTSMCの設計協力会社組織であるTSMCデザインセンタアライアンス(ACA)メンバーであると同時にTSMCバリューチェーンアグリゲータ(VCA)認定企業でもあり、TSMCとの結びつきが強い。同社は、2003年に日本とシリコンバレーの設計技術者が共同で設立したベンチャーで、日本にもデザインセンターがある。

TSMCの5nm EUV製造ラインは、現在、次世代Apple iPhone用およびHuawei Mate 次期5Gモデル用5nmアプリケーションプロセッサの量産で埋まっているが、それが間もなく一段落すれば、他社の5nmデバイスの製造も受託可能になる。

Alchipは、5nmの設計から納品までのターンアラウンドタイムを最小限に抑えることに重点を置いており、設計に際しては、チップレットテクノロジープラットフォーム、高性能コンピューティングIPポートフォリオ、IPサブシステム統合サービス、最新の2.5D異種パッケージング機能が活用できるとしている。

同社は、5nmの最初の需要は、高性能クラウドコンピューティングアプリケーションから生じると予想している。現在の7nmデバイスと比較して、5nmデバイスは面積が52%小さく、演算速度が3%速く、しかも電力は7nmデバイスに比べて36%程度に抑えられると予測している。同社は5nm設計に、最先端のDDR5、GDDR6、HBM2E、HBM3、D2D、PCIe5、Tier 1プロバイダの112G SerDes IPを含む高性能コンピューティングIPポートフォリオを利用している。Alchip社内IPサブシステム統合サービスは、PCIe5、DDR5、HBM2E/3、および112G PAM4 SerDesをカバーしている。

また、5nmで求められるのはMCM、CoWoS、およびInFO_os向けの高度なパッケージング機能で、顧客の要望に応じていずれも使用可能としている。

GREEN500トップの日本製スパコンのプロセッサの設計を支援

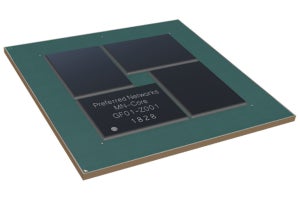

2020年6月に発表された、世界でエネルギー効率の高いスーパーコンピュータ(スパコン)のランキング「Green500」において、日本のPreferred Networks(PFN)と神戸大学が共同開発したディープラーニングプロセッサ「MN-Core」を搭載したPFN製スパコン「MN-3」が1位を獲得したが、AlchipはPFNのスパコン用プロセッサ設計を支援したことも明らかにした。

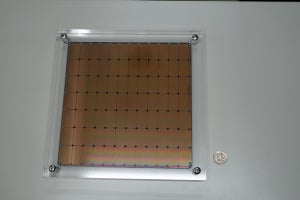

MN-Coreは、技術的に機械学習の最先端に位置し、面積800mm2という巨大な4個のダイを搭載して、独自のダイツーダイインタフェーステクノロジーを組み込んだ高度な省電力マルチチップパッケージとして設計されているが、Alchipは、このASICの物理設計と試作・製造(TSMCへ製造委託)を担当したという。

MN-Coreは、ディープラーニングに特有の行列演算用に最適化されており、ワットあたり1TFLOPS(半精度)の世界トップクラスのエネルギー効率を実現した。MN-3には、このMN-Coreが4つ搭載されている。Green500ランキングで1位を獲得するために、PFNは40ノード(合計160 MN-Core)を運用し、21.11GFLOPS/Wを達成した。

Alchip CEOであるJohnny Shen氏は、「MN-Coreは複雑なフルレチクルサイズのSoCであるため、多くの設計上の課題が生じた。500Wの消費電力で生じる熱も大きな課題だった。また、このような大きなチップをマウントすることの信頼性の懸念を排除するために、早い段階でメカニカルパッケージサンプルを開発する必要もあった。この複雑なテスト設計は、プロジェクトの厳しいスケジュールを考えると、特に困難だった」と述べている。また、「高性能コンピューティングASICは、TSMCのプロセステクノロジーに基づいて構築されている。4個のチップは85mm×85mmの有機基板上に配置されている。小さな面積/電力比で帯域幅の需要を提供するAlchip独自のD2D(ダイツーダイ)インタフェーステクノロジーを採用しており、Alchipはチップとパッケージの統合と検証を提供した」ともコメントしている。

なお、PFN執行役員計算基盤担当VPの土井裕介氏は、「Alchipの持つ先端LSI(大規模集積回路)開発技術は、『MN-Core』開発において大きな役割を担いました。特に、深層学習において必要となる行列計算を高密度・低電圧に実装するための技術は必須でした。PFNはAlchipの協力により開発したMN-Coreを用いて、さらなる深層学習の研究開発を進めていきます」とコメントを寄せている。

2020年8月18日訂正:記事初出時、PFNの土井裕介氏の役職を副社長と誤って記載しておりましたが、正しくは執行役員計算基盤担当VPとなりますので、当該部分を訂正させていただきました。また、併せてコメントの記載内容も修正させていただきました。ご迷惑をお掛けした読者の皆様、ならびに関係各位に深くお詫び申し上げます。