東京大学、凸版印刷、パナソニック、日立製作所、ミライズテクノロジーズは8月17日、「先端システム技術研究組合(略称:ラース、RaaSと表記)」(理事長 黒田 忠広 東京大学大学院工学系研究科附属システムデザイン研究センター長 教授)を設立すると発表した。RaaSは、データ駆動型社会を支えるシステムに必要な専用チップのデザインプラットフォームを構築し、オープンアーキテクチャを展開することで、専用チップの開発効率を10倍高める。また、3次元集積技術を研究開発し、最新の7nm CMOSで製造したチップを同一パッケージ内に積層実装することで、エネルギー効率を10倍高めるという。

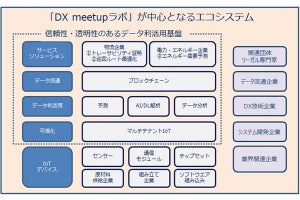

5者によると、デジタルトランスフォーメーション(DX)の実現するためにはフィジカル空間(現実空間)とサイバー空間(仮想空間)をシームレスにつなぐデータの活用が必要であり、IoTデバイスでセンシングしたデータを5Gで集め、AIで高度な分析を加えてサービスとして提供する、データ駆動型社会を支えるシステムが求められているという。

デジタル技術はプラットフォームで発展・普及するため、従来のコストパフォーマンスに加え、タイムパフォーマンスが重要になり、安く高性能であるだけでなく、素早く提供することも重要であることから、専用チップを最先端プロセスで製造すると高い性能を得ることができるものの、開発には多大な費用と年月を要することが課題だった。

RaaSは、東京大学、凸版印刷、パナソニック、日立製作所、ミライズテクノロジーズ(デンソーとトヨタ自動車の合弁会社)の5組合員で活動を開始し、各社の事業領域(ドメイン)で求められるシステムをテーマにデザインプラットフォームを共同で研究開発する。加えて、半導体産業界のエコシステムを支えるファブレスSoC事業会社(ソシオネクストなど)やEDAベンダーが活動を支援する。

RaaSの研究開発目標は、専用チップの開発効率を10倍高めると同時に、エネルギー効率を10倍高めることとしている。開発効率を高めるために、専用チップを素早く設計できるアジャイル設計手法を研究開発し、オープンアーキテクチャを展開する。

さらに、エネルギー効率を高めるために、3次元集積技術を研究開発し、世界のメガファウンドリ(半導体デバイスを生産する工場)で7nm CMOSで製造したチップを同一パッケージ内に積層実装する。例えば、複数のSRAMチップを3次元集積してDRAM並みに大容量の積層SRAMを実現し、タイミング設計の難しいDRAMに代えて積層SRAMを用いることで、コンピュータを用いた自動設計で設計効率を改善する。

加えて、積層SRAMと専用チップを同一パッケージ内に積層実装することで、エネルギー効率を改善し、デザインプラットフォームを活用して、各組合員は実現したいシステムを開発して事業化する。