世界に変革をもたらしてきた「スケーリング」

半導体の分野では「スケーリング」という用語をよく目にします。たとえば、ナノスケールの構成要素の寸法を原子スケールにまで縮小するという、トランジスタのスケーリング(微細化)に関する見出しを業界ニュースで見たことがあるかもしれません。あるいは、私たちが日々使用しているモバイル機器で高解像度の動画を保存できるようにするメモリ容量のスケーリング(拡張)について聞いたことがあるかもしれません。いずれの内容も、スケーリングはほとんどの場合「進歩」を意味します。

そうした進歩は、デバイスのフットプリント削減、3次元構造による拡張、新素材や革新的なアーキテクチャの採用によって実現されています。現代のデジタル社会は、そのような技術の発展で成り立っているのです。年月を経て、日常生活のあらゆる面を劇的に変えたデバイスが微細化によって生み出され、指先一つで膨大なデジタル情報を得られるようになりました。

トランジスタのスケーリング(微細化)

半導体の微細化については、ムーアの法則でよく知られています。もともとは経済的合理性に関するもので、18か月から24か月でチップの素子数が倍増すると予測した法則です。

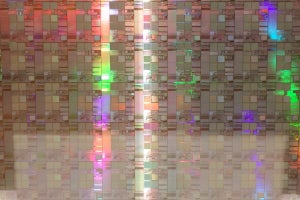

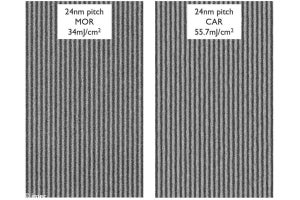

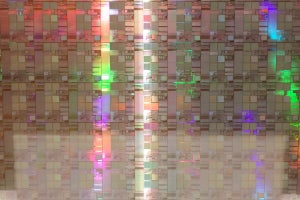

この数十年間、ウェハの表面にパターンを焼き付けて加工するリソグラフィとプラズマエッチング工程における進歩によって、半導体業界は重要な(あるいは不可欠な)トランジスタという構成要素を縮小し、発展を遂げてきました。

そして半導体のテクノロジーノードは、一般的にトランジスタのゲート長を指す言葉でした。例えば、0.5μmのテクノロジーノードとは、ゲート長0.5μmのトランジスタを意味しました。しかし、時代とともにテクノロジーノードの定義は変化し、現在はこうしたトランジスタに関する主要な部位の寸法指標としてではなく、単にデバイスの世代を表す名称として用いられるようになっています。しかし、ノードの微細化によってデバイスの性能と電力効率が向上し、製造コストの削減につながるという考え方に変わりはありません。

高性能トランジスタは、約20nmのノードで微細化の限界に達しました。半導体業界のエンジニアは、プレーナ型トランジスタの水平寸法を縮小すると他の問題が生じることから、他のトランジスタ設計方法を模索せざるを得ませんでした。

3次元のFinFET構造では、シリコンウェハに対しトランジスタの主要な構成要素が立体的に配置されるため、トランジスタのチャンネル容量を減少させることなく、デバイスのフットプリント削減が可能です。FinFETの微細化では、デバイス性能を向上させる方法として、フィンの高さを高くすると同時に、ユニット面積当たりのデバイス密度を高めるために水平寸法を縮小しています。

トランジスタの微細化を継続させ、高性能で低電力消費かつ低コストのデバイスを実現するために、近年はシリコンにゲルマニウムを含ませていますが、FinFET技術で5nmのノードを超えるには新しい素材が必要かもしれません。または、積層ナノシートやナノワイヤなどの新しいアーキテクチャが解決策となる可能性があります。それらの構造の加工には、ほぼ間違いなく、微細化を図るために原子層レベルの成膜とエッチング工程の活用が必要になります。

コンタクト層のスケーリング(微細化)

トランジスタの寸法が縮小すると、トランジスタと配線層を接続するために必要なコンタクト層の寸法も全体的に縮小させる必要があります。世代が進み、そうした局所的なインターコネクトが高密度化するなか、さらに微細化を進めると現在主流の銅配線では重大な課題に直面します。例えば、配線の幅や高さをさらに減少させると、配線の電気抵抗が大幅に増大します。半導体製造メーカーは、銅の汚染などを防ぐことができる高い抵抗率を有する新たなバリア材料やライナー材料を活用しつつ、バリア層やライナー層のスペースの削減を目指しています。もう1つの可能性は、銅の代わりにバリア層を必要としない別の金属を使用するか、そうした金属で銅を合金化することです。

メモリ容量のスケーリング(拡張)

3D NANDのメモリ容量のスケーリングは、垂直方向の積層という別の方法で実現されています。このメモリ構造では、セル密度が積層数に比例して増加します。初期の3D NANDでは24層構造が用いられていましたが、今では96層や128層構造のチップが量産され、積層数のさらなる増加が見込まれています。各層は均一かつ滑らかで、下層にしっかり接着されている必要があり、積層数に伴い課題も増えます。

層の追加による継続的な容量のスケーリングは、高アスペクト比のメモリホールのエッチング、ステアケースのパターン定義、ワードラインのタングステン埋め込みなど、その後に続く工程を複雑にします。また、チャンネル長が長くなると、電子移動度が制限されてデバイスの性能に影響を及ぼします。目下、重要な成膜工程とエッチング工程が今後の世代を確実にサポートできるようにする取り組みが進められています。

まとめ

現在の最先端チップは、これまでに設計・製造されてきたものの中でほぼ間違いなくもっとも高度なデバイスであり、数十年にわたるスケーリングの取り組みの直接的な成果といえます。水平方向のサイズを縮小し、縦方向に積層を図る現在のデバイスに求められるパフォーマンスとコストのメリットは半導体製造装置の進歩と、製造装置メーカーとチップメーカーの連携強化によって実現できるものとなってきています。

半導体のスケーリングによって、私たちの仕事、通勤、娯楽、通信の方法は変わりました。イノベーションの方向性としては「モア・ムーア(More Moore)」が続くことが期待されています。半導体業界の発展を支えるもう1つの方向性として、多種多様な技術をさまざまなアーキテクチャやシステムに取り入れる「モア・ザン・ムーア(More than Moore)」戦略も注目を集めるようになっています。

今後は、この2つの方向性を同時に進めていくことが、よりスマートで、よりコネクテッドな社会の実現を推進するために必要となるスピードやパフォーマンスをより多くの分野に提供するために必要となっていくでしょう。

著者プロフィール

Nerissa Draeger(ネリッサ・ドレーガー)Lam Research

グローバル大学教育エンゲージメント・ディレクター

ラムリサーチのテクノロジーおよび人材開拓における多様性を創出のため、外部との共同研究や学術的なパートナーシップを通じて、半導体製造の革新的なソリューションを推進。

成膜技術、表面科学の分野で20年以上の経験を有し、これまで30以上の特許を取得。また、数多くの技術記事を執筆。

カリフォルニア大学バークレー校

エンジニアリング・リーダーシップ・プロフェッショナル・プログラム 修了

イリノイ大学アーバナ・シャンペーン校 材料科学および工学(博士課程)