TSMCは、先端高密度半導体実装技術「ファンアウト・ウエハーレベルパッケージ(FOWLP)」の同社独自の呼称である「Integrated Fan-Out(InFO)」をベースに、複数のチップを積み上げる「Multi-Stacking(MUST)」技術を3次元実装技術として開発してきたが、今度はこれを応用して5Gスマートフォン(スマホ)向けに、InFO実装したRF-FEM(フロントエンド・モジュール)チップの上に複数のアンテナを搭載し1つのパッケージに収納したINFO_AiP (Integrated Fan-Out Antenna in Package)技術を開発し、中国の華為技術(Huawei)が2020年下半期に発売する予定の5G対応フラッグシップスマホに搭載するする見通しだと、台湾の経済メディア中国時報の電子版である中時電子報(中国語版)が4月27日に伝えた。

Appleが2020年秋に発売すると見込まれるiPhone 12(仮)にはTSMCのInFO_AiPプロセスを使用しない独立したアンテナが搭載されると見られているが、Huawei(ならびに同社子会社のIC設計会社のHiSilicon)は、TSMCのInFO_AiP技術を使用するアンテナモジュールを、積極的に採用する計画であり、これによりiPhoneより薄型化を図るとしている。

AppleやHuawei、Samsungといったトップブランド各社が開発を進めている5Gスマホは、消費電力を削減し、薄型、軽量という目標を達成するために、多数のSiPを活用しており、TSMCも、そうした顧客ニーズに応じるために独自の実装技術の開発と提供を売り物にするようになっている。

InFOからInFO_AiPに至る技術動向は?

近年の半導体実装技術の進歩は目覚ましく、非常に複雑になっていることもあるので、InFOからInFO_AIPに至る技術動向を噛み砕いて説明してみたいと思う。

InFO(FOWLP)とは?

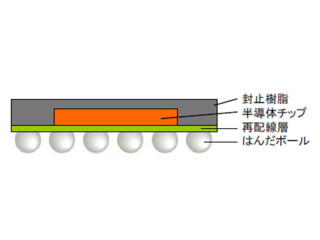

FOWLPの概略図を図1に示す。半導体チップの端子から配線を引き出す再配線層をウェハプロセスを用いて形成することで、パッケージ基板をやめて、ワイヤもバンプもなく、製造費用を安く、厚みを薄くできるようになる。再配線層は薄膜のため配線長を短くできるので、電気信号の伝送速度を高速化できる。

従来のWLCSP(ウェハレベルチップサイズパッケージ)がパッケージ面積と半導体チップ面積が同じであるのに対して、FOWLPはチップの外側まで端子を広げるためパッケージ面積が半導体チップより大きく、多ピン対応が可能で、微細化によるチップの小型化にも対応できる。

InFO_PoPとは?

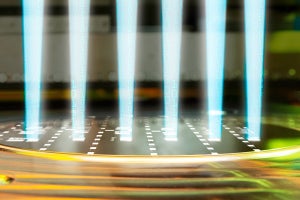

InFO技術を用いて実装した半導体チップの上に別の半導体チップを積層した3次元実装が「InFO PoP(Integrated Fan-Out Package on Package)」である(図2)。製造コストが高いTSV(シリコン貫通ビア)を用いず複数の半導体チップを垂直方向に積層して小型化を図るSiPのプラットフォームである。

TSMCは、5G対応スマホ向けアプリケーションプロセッサ(AP)とモバイルDRAMをInFO_PoPプロセスを用いて1つのパッケージに収納する実装技術を以前から顧客に提供している。

InFO MUST

5G用チップでは、コンピューティングパフォーマンスを向上させるために、より広い帯域幅のメモリサポートが必要であるが、メモリチップのI/Oが障害となる。

このため、AP/BBを高密度再配線層を介してDRAMに直接接続するMultiple Stacking(MUST)実装が開発されている。メモリパッケージには、プラスティック基板やはんだボールが不要なのでメモリとAP/BB間の距離が短縮され、PI・SI(信号整合性・電源ノイズ)が改善される。

InFO_AiPとは?

InFo MUSTの応用として、5G通信向けにInFO技術で実装したミリ波RF-FEMチップ上に複数のアンテナ(ダイポールアンテナやパッチアンテナ)を搭載し1つのパッケージに実装したものがInFO_AiP(InFO with antenna in Package)である。AiPパッケージは、アンテナを含んだパッケージのサイズと厚さを削減できるとともに、高利得・低損失のアンテナ性能が得られる(図4、5)。