ムーアの法則は終わったのか?

米国の半導体市場動向調査会社であるIC Insightsは、過去50年間にDRAM、NAND、APU、GPUがムーアの法則(Moore's Law)にどのようにしたがってトランジスタ数を増加させてきたのかについての調査分析結果を発表した。

ムーアの法則(Moore's Law)は、半導体業界がその技術的性能と進歩を測定する主要な物差しとして長年にわたり使われてきた。それは「チップあたりのトランジスタ数が2年で2倍のぺースで増加する」という経験則であるが、分析結果によると、一部の製品カテゴリの成長率は低下しているとは言うものの、チップあたりのトランジスタ搭載数の「2年で2倍の増加ペース」は現在もおおむね継続しており、半導体業界が引き続きしたがうに足るガイドラインとなっているという。

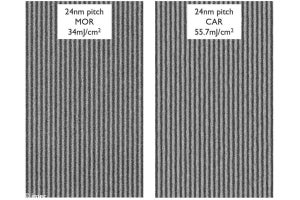

ムーアの法則は、3次元構造デバイスが登場するまでは、チップ当たりのトランジスタ数の増加すなわち、それを実現するための加工寸法(プロセス)の微細化の法則といった見方もできたが、いまではプロセスの微細化に加え、3次元化でもトランジスタ数は増加できるため、デバイスの構造も使用される材料も大きく変化してきている。次世代半導体デバイスの開発を主導するベルギーimecは、ムーアの法則を継続させるために、プロセスの最適化だけではなく、「回路設計」、「プロセス」、「システム」の3者を同時に最適化する手法を編み出している。

各デバイスごとの動向

DRAM

消費電力や比例縮小の困難な課題に直面して、一部のIC製品のトランジスタ搭載数の成長率は過去10~15年にわたって低下を続けてきた。

例えばDRAMのトランジスタ数は、2000年代初頭までは年間平均約45%の勢いで増加していたが、その後2016年に登場した16Gビット世代までの間に約20%に低下した。Samsung Electronicsは、2014年に8GビットDRAMチップ、2015年に12GビットDRAMチップ、そして2016年末に16GビットDRAMチップの量産を始めた。JEDECによって最終決定されつつあるDDR5スタンダードには、モノリシック24Gビット、32Gビット、および64Gビットデバイスが含まれているので、いずれ順々で量産されることになるだろう。

NAND

NANDフラッシュメモリ容量の年間成長率は、2012年ころまで年間55〜60%であったが、その後は年間30〜35%程度となっている。従来の2D NANDの場合、2020年1月時点で単一ダイの最大容量は128Gビットであるが、3D NANDの最大容量は、96層のクワッドレベルセル(QLC)の1.33Tビットである。QLCと多層化技術を組み合わせることで、3D NANDの最大容量は1.5Tビットとなり、128層技術を適用すれば2Tビットも実現できる。

マイクロプロセッサ

IntelのPC用マイクロプロセッサ(MPU)のトランジスタ搭載数は、2010年までは年平均約40%の増加で推移してきた。その後、その割合は半減している。Intelのサーバ向けMPUのトランジスタ数の伸びは、2000年代半ばから後半に一時的に止まったものの、その後、約25%/年の割合で再び増加し始めている。なお、Intelは2017年にトランジスタ搭載数の詳細な公開を行わなくなった。

アプリケーションプロセッサ

iPhoneおよびiPadで使用されているAppleのAシリーズアリケーションプロセッサ(APU)のトランジスタ数は、2013年以降、85億個のトランジスタを搭載したA13プロセッサまで43%/年の割合で増加している。

GPU

NVIDIAのハイエンドGPUは他社のプロセッサに比べて多くのトランジスタを搭載しているが、マイクロプロセッサとは異なり、GPUの高度な並列構造には、大量のキャッシュメモリが含まれていない。また、NVIDIAの一部の最新GPUは、AIと機械学習向けに特別に設計されたニューラルネットワーク処理ユニット(NPU)であるといえる。

ムーアの法則は今後も成り立つのか?

なお、IC Insightsは、今回の分析結果を踏まえて、「技術の障壁を越えて革新を目指す半導体産業の推進力としてムーアの法則は今後も決して過小評価することはできない。ICの設計および製造方法に関して、いくつかの非常に劇的な変化が進行中であることは事実であり、将来の世代に向けた性能向上を妨げる障害のいくつかは、ハードルというよりも高い壁のように見えるのも事実。しかし、半導体業界は、そうした壁を乗り越えてムーアの法則を維持し続けるだろう」と述べている。