半導体ハイテク研究機関のベルギーimecは、同国のゲント大学と共同でPAM-4変調を使用して消費電力700mWで最大100Gbaud(200Gb/s)の信号速度を達成する高速シリコンアナログタイムインターリーバーを開発し、米国サンフランシスコで開催された半導体の国際学会「ISSCC 2020」にて発表した。

タイム・インターリーブ方式は、同一のA/Dコンバータ(ADC)を複数使用することで、1個のADCでは対応できないより高いサンプル・レートを実現する手法である。今回の新しいアーキテクチャは、将来のデータ爆発に対応可能なデータセンタの高速光トランシーバの重要な構成要素を目指して開発したとしている。

データ爆発に対応するため、近年、データセンタでは、光ファイバーケーブルの階層ネットワークを介してサーバーラックを相互接続する光リンクが増えている。これらのリンクは低コストで低電力である必要があるが、少なくとも100Gbaudまで信号速度を高速化する必要であるとimecでは説明している。

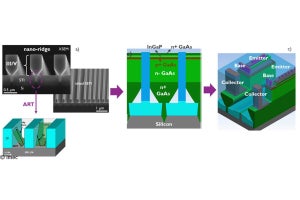

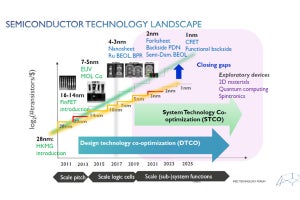

こうした高速光トランシーバーは、これまでInP基板を用いる必要があったが、InPプロセスは製造コストが高いため、大規模生産には向いておらずより安価なSiベースのCMOSプロセスでの実現が求められていた。

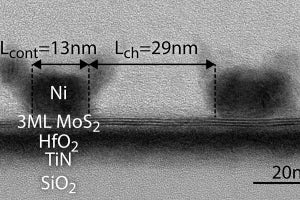

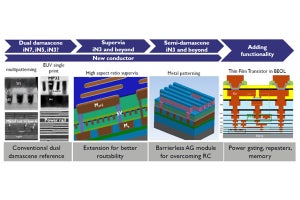

しかし、SiベースのCMOSプロセスではアナログ帯域幅が限られているため、所望の高速を実現できず、D/Aコンバータ(DAC)の帯域幅が50GHzを超えることは難しかった。そこで研究グループは今回、55nm SiGe BiCMOSテクノロジーを使用して、より高い帯域幅を達成することに成功したという。

このBiCMOSチップでは、4つのDACの出力が結合され、4つの25Gbaudストリームをタイムインターリーブすることにより、100Gbaudの信号速度を実現したという。

これは、100GSpsで動作する単一のDACと同等性能であり、PAM-4変調フォーマットを使用すると200Gbpsのデータレートが得られたにもかかわらず、プロトタイプの総消費電力は700mWに抑えられることも確認したとしており、研究グループでは、Si同様、SiGe BiCMOSテクノロジーはスケーラブルに大量生産に適用できるため、次世代データセンタ向けに費用対効果の高い高速光トランシーバを提供するための道が開かれた、と説明している。