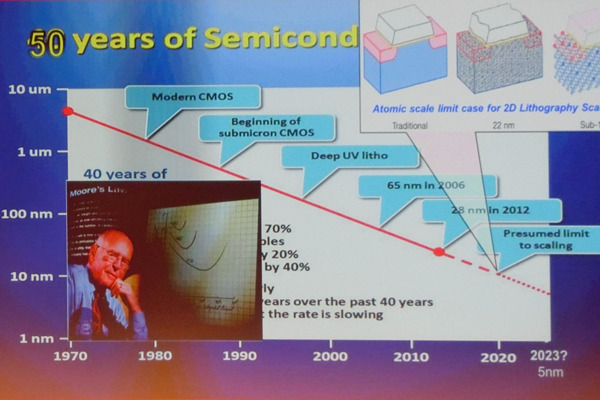

TSMCは、2019年12月に米カリフォルニア州サンフランシスコで開催される半導体デバイスに関する国際会議「IEDM(2019 IEDM)」にて、モバイルデバイスと高性能コンピューティング(HPC)向けに最適化された最先端となる5nm CMOSプロセスプラットフォームに関する講演を行うことが、IEDMが公開した「Late News Paper」から明らかになった。

TSMCの5nmプロセスは、従来の7nmプロセスに比べて、ロジック回路密度がほぼ2倍(正確には1.84倍)、速度が15%向上(消費電力が同じ場合)、そして消費電力が30%削減(速度が同じ場合)という性能を発揮するという。

すでに同社は7nmの改良版である7nm+プロセスからEUVリソグラフィを採用しているが、5nmではさらに多くのレイヤにEUVを適用しており、5枚分の液浸ArFリソグラフィ用マスクがEUVマスク1枚で置き換えられるため、使用マスク数は7nmプロセスの場合より減少できたとしている。

また、5nmプロセスでは、完全歪み高チャネルモビリティFinFETを採用し、駆動電流が18%向上したほか、業界最高クラスの高密度SRAMセルを採用したとしており、しかもこのSRAMは、低電力用途であるか高性能用途であるかに応じて最適化することができ、そのSRAMセル面積は0.021μm2であるという。

さらに、テストデバイスでの測定では、高速データ通信に使われるPAM4トランスミッタで0.96pJ/ビットのエネルギー効率と130Gbpsの伝送速度を実証したとする。

なお、TSMCは、同社のプライベートセミナなどで、新しいlow-k材料、Cuダマシンプロセスに替わる金属反応性イオンエッチング(RIE)、グラフェンキャップを用いたCu相互接続の抵抗率低減を5nmプロセス以降に向けたプロセスとして検討していることを明らかにしているが、これらについては、今回のIEDMからの発表では触れられていない。TSMCは、この5nmプロセスを用いた受託生産(量産)を台湾台南市のFab18で2020年第2四半期に開始する予定で、2020年秋に発売されるであろう次世代のApple iPhneに搭載されると思われるA14プロセッサや、競合となるHuaweiの製品が同プロセスを採用することが予想される。

TSMC以外のLate News Paper

今回、IEDMが明らかにしたLate News Paperには、TSMCの5nmプロセス以外にも、以下のようなテーマも掲載されている。

- Intel:ヘテロジーニアス3次元スケーリング技術(Si基板上に形成したSi FinFET NMOSの上にウェハ張り合わせでGe層を形成しそこにGate-All-Around(GAA) GeチャンネルPMOSを積層し3次CMOSを実現)

- CEA-Leti:高エネルギー密度を実現した薄膜バッテリ

- STMicroelectronics:400Gbpsデータ送信のためのシリコンフォトニクスプラットフォーム

- 人工知能(AI)などに活用可能なエンベデッドMRAMに関する各研究機関からの複数の論文

- AI、量子コンピュータ、ヒューマン・マシン・インタフェース、回路/システム信頼性などのホットトピックスに関する特別セッションの論文群