ベルギーimecのロジックデバイス設計チームは、5月14~15日に開催された同社の年次イベント「Imec Technology Forum (ITF) Belgium 2019」に併せて、半導体ロジックデバイスの微細化ロードマップを更新した。

今回のアップデートでは、技術ノードは新たにiN7~iN1のように表現された。この頭文字のiはimecを意味し、Nは技術ノード(Technology Node)を、7や1は微細化の指標で従来は7nmとか1nmと表現されていたが、実際は物理的な長さを示すものではなかった(()内のCPPはContacted Poly Pitch(コンタクトを有するポリシリコン配線のピッチ)、Mxはメタルピッチを表す)。

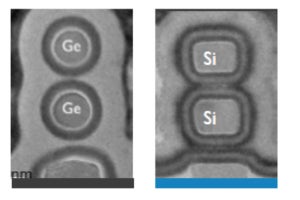

今回公開されたロードマップでは、iN7まではFinFETが使用され、iN5からiN3まではGAAナノシートの積層構造が採用されるという。ただし、高性能用途や低消費電力用途では改良版のFinFETが採用されるとしている。iN2では、N型P型のナノシートを近接して配置したForksheet、CMOS構成のComplementary FET、Geナノワイヤ、Ge FinFETなど様々な選択肢が考えられる。iN1およびそれ以降では、CMOSを超えた新たなデバイス概念、新しい機能、システム、アプリケーションが出てくるだろうから、微細化の限界については予測しがたいという。

imecでは、トランジスタ構造の微細化に加えて、3次元相互配線構造の高密度化にも取り組んでおり、3D SiP(System in Package)、3D SIC(Stacked IC:ダイの積層)、3D SoC(System on Chip)を経て3D IC(トランジスタ自体の積層化)に向かうとしている。また、3次元相互配線技術の進化により、3D 相互配線のピッチの微細化指標(nm)および3次元相互配線密度(#/mm2)も微細化していく。今までは3次元相互配線微細化は3D SiPが担当してきたが、今後はLogic Programが直接担当するという。