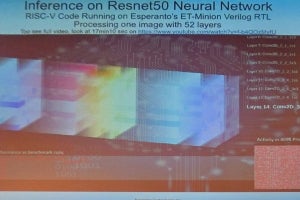

RISC-V Dayでは、Esperanto社のPolychronis Xekalakis氏がET-Maxionプロセサについて発表を行った。

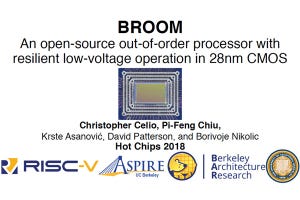

ET-Maxionコアはカリフォルニア大学バークレー校のBOOMコアをベースにして開発を行った。BOOMは比較的簡単なOut-of-Orderコアで、I/Oなどの周辺はRocketコアのものを流用している。BOOMを実装したBROOMチップはすでにできており、Linuxをブートしている。性能はArmのCortex-A15と同程度である。

Esperanto社では、このBOOMコアをベースに次のような改良を行った。

- クロック周波数の引き上げ

- 分岐予測とプリフェッチを最先端のものに改良

- 命令のフェッチ、デコード、発行の幅の拡大

- 命令、データキャッシュとTLBのサイズの拡大とECCの付加

- 圧縮命令の追加をサポート

- フロントエンドとロード、ストアユニットの再設計

- デバグ回路の改良

- パフォーマンスモニタの改良

-

Maxionはバークレー校のBOOMコアをベースにしているが、クロックの向上や同時実行命令数、分岐予測の高度化など、大幅に改良が加えられている (このレポートの図は、RISC-V DayにおけるEsperanto社のXekalakis氏の発表スライドを撮影したものである)

MaxionはTSMCの7nmプロセスを使い2GHz程度のクロックで動作する。フェッチからライトバックまでのパイプラインは10段であり、フェッチに4段、アロケートとリネームに2段、ディスパッチとレジスタファイルの読み出しに2段、実行とライトバックに各1段という配分である。そして、ロード命令から、読み出した値が使えるようになるまでのロードユースレーテンシは4サイクルとなっている。

メモリサブシステムは64KBの1次データキャッシュと4MBの2次キャッシュを持つ。そしてアグレッシブなプリフェッチを行う。これらのキャッシュはECC付きである。また、32エントリのdTLBと1KエントリのL2 dTLBを持つ。

命令フェッチ系は2Kエントリの圧縮BTBを持つ。そして、32KBのECC付きの命令キャッシュを持ち、4KエントリのiTLBを持っている。そして、条件分岐予測やパスに基づく分岐予測機構を備えている。

実行系は、64エントリの分散型のスケジューラを持ち、128エントリのリオーダバッファ、32エントリのロードキュー、32エントリのストアキューを持つ。

整数レジスタファイルは8R4Wで128エントリ、浮動小数点レジスタファイルは3R2Wで64エントリである。

整数のパイプラインは、ロード/ストア命令1本、単純なALU命令2本、複雑なALU命令/分岐が1本となっている。この図では浮動小数点の実行パイプラインについては説明されていないが、次のパイプラインの図では浮動小数点処理のパイプラインは1本で、演算の実行は3サイクルとなっている。

RISC-Vの命令セットとしては汎用のRV64G命令セットの機能に加えてデータ圧縮拡張、特権命令拡張をサポートしており、リラックスドメモリモデルと外部からのデバグ仕様もサポートしている。

Maxionのパイプラインは次の図のようになっている。デコードから実行、リタイヤまで最大4命令を並列に処理することができる。なお、元になったバークレー校のBOOMコアは2命令並列であるので、Maxionは大幅に性能強化された設計になっていることが分かる。

なお、10段のパイプラインとなるのは単純なALU命令の場合で、演算に3サイクルかかる浮動小数点演算命令を実行する場合は、13段のパイプラインとなっている。

次の図はMaxionコアのフロアプランを示すものである。HPFプリフェッチユニットはアグレッシブな処理を行い、L2キャッシュのアクセスレーテンシを隠すことができる。分岐予測を行うBPUは直接分岐と間接分岐でそれぞれに最適化された予測機構を使っている。また、レジスタファイルに面積を割き、多数の物理レジスタを持たせている。大きなデータキャッシュを入出力パッドに近い位置に配置し、消費電力を抑えている。などなど、性能と消費電力に配慮したフロアプランになっている。

Maxionの性能見積もりであるが、次の図ではSPECint2K/GHzとクロック周波数を比較している。5本の棒グラフがあるが、左から、インオーダのRISC-VであるRocketコア、Boom v2、Maxion、ArmのCortex-A57、ArmのCortex-A72となっている。

MaxionはSPECint2KではA57と並び、A72よりは若干性能が低い。また、クロックではA57より若干上回り、A72には若干劣るという比較になっている。

-

Maxionの性能見積もり。棒グラフは、左からバークレー校のRocketコア、BOOM v2、Maxion、Arm A57、Arm A72コアのSPECint2K性能/MHz(左)とクロック周波数(右)

Maxionの設計はプレシリコンのバリデーションに大きく依存しているが、シミュレーションやFPGAでは再現できない複雑な問題をデバグするため、特定のシーケンスでトリガを掛け、内部状態の波形を観測するようなデバグ機構を設けている。また、複数の事象の発生をカウントする性能カウンタも備えている。

Esperantoは、SpectreやMeltdownが利用しているタイミングアタックには注意を払っている。これらのアタックは投機的な動作の影響がタイミングアタックで読み出されてしまうことで起こる。このため、EsperantoのCPUでは、分岐予測機構の状態を投機的に更新することは行わない。また、キャッシュも投機的な更新は行わない。また、プリフェッチ機構も、投機的な更新は行わないという対策をとっている。これらの対策による性能の低下は小さく、同時に、タイミングアタックをかなり難しくすることができているという。

なお、Minionコアは投機実行を行っていないので、SpectreやMeltdownの攻撃には影響されないので対策は不要である。

Maxionは、RISC-Vのシンプルなアーキテクチャに基づいているので、高いクロック周波数を比較的少ない努力で実現できている。そして、努力の大半は、BOOMの機能の安定性の改善、パイプライン構成をチューニングしてクロックを上げること、性能改善機構のチューニングなどに充てることができた。また、BOOMが備えていない商用プロセサの各種機能の実装の実装に力を注いだ。

結果として、Maxionはハイエンドのarmコアと競争できるレベルの初めてのRISC-Vコアとなった。

-

簡潔なRISC-V ISAに基づく設計であるので、基本的な機能の実現には、あまり手間は掛からない。そのため、BOOMの機能の安定性の改善やBOOMが持っていない商用コアとして必要な機能に開発努力をつぎ込んだ。結果としてMaxionはArmのハイエンドコアに匹敵する初めてのRISC-Vコアとなった

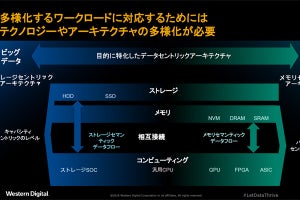

Armでさえもデータセンター市場への食い込みには苦戦している状況であり、EsperantoのRISC-Vプロセサにとっても難しい戦いになると予想される。しかし、Esperantoのシステムは4Kコアという大量のMinionコアでAI処理を行うというものである。また、MinionはAI専用ではなく、汎用のアクセラレータコアであり、他の用途にも進出が可能である。このような特徴を生かしてのEsperantoの健闘を祈りたい。