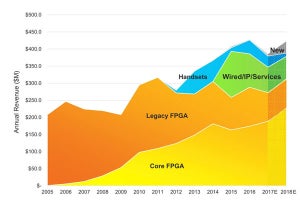

Lattice Semiconductorに日本法人であるラティスセミコンダクターは10月11日、都内で9月25日(米国時間)に発表したsensAIスタックの拡張に関する説明会を開催。小型FPGAによるAI活用の分野が拡大していくことをアピールした。

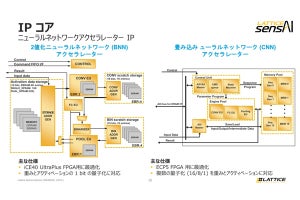

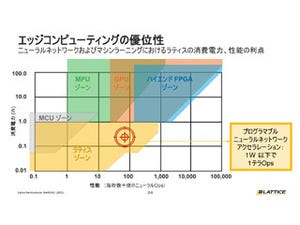

sensAIは、2018年5月より提供を開始した同社のFPGA(iCE40 UltraPlus/ECP 5)向けニューラルネットワークIPと開発環境をパッケージ化したソリューション。これまで回路規模の小さなiCE40 UltraPlus向けにはBNN用IPが、比較的回路規模が大きいECP 5にはCNN用IPが提供されてきた。

提供開始から約半年を経て、顧客の要望などを受ける形で、今回、iCE40 UltraPlus向けに6ビットと1ビットの量子化に対応したCNNアクセラレータIPが提供されるようになったほか、ECP 5向けのCNNアクセラレータIPも、DRAMのメモリ帯域幅を従来の16ビット幅から32ビット幅に拡大することで、DRAMへのアクセス速度向上を可能とする機能強化が図られた。

また、iCE40 UltraPlusのCNNへの対応に併せて、フレームワークもCaffeとTensorFlowの両方にニューラルネットワークコンパイラを対応させた(従来はCaffeのみ)ほか、提供されるリファレンスデザインとして、新たに人感検出とハンドジェスチャ認識をiCE40 UltraPlus向けに、パートナー企業であるWiproから荷物検出が、同じくSoftnauticsからは車種識別がECP 5向けに提供されるようになった。

-

併せて,従来、Caffeへの対応のみであったiCE40 UltraPlusがTensorFlowにも対応した (出典:Lattice Semiconductor)A@CaffeとTensorFlowの両方に対応

さらに、開発の容易化に向け、新たにHiMaxのHM01B0搭載UPDuinoシールド、 dpcontrolのiCEVisionボードといったiCE40 UltraPlus開発プラットフォームも提供が開始(UPDuinoシールドは2018年11月より提供開始予定)されるほか、

加えて、パートナー企業によるニューラルネットワークのトレーニングや開発、RTLによる回路設計といったカスタムデザインサービスにも、今回新たにポコアポコネットワークスと三栄ハイテックスが追加。これにより、日本のカスタマは、よりコミュニケーションなどを活発に行い、開発を加速させることが可能になったとのことで、「iCE40 UltraPlusのCNNアクセラレータIPも従来のBNNアクセラレータIPと同程度のLUTを使用するので、CPUを搭載するには、RTLを記述する必要があったが、国内パートナーの誕生により、そうした取り組みもしやすくなる」とラティスセミコンダクターで技術責任者を務める崎田寛明氏は説明する。

なお、今後のロードマップについて、崎田氏によると、「RNNについてはニーズはあるものの、搭載メモリの容量不足などの問題もあり、計画はない。ただし、2019年以降の出荷予定となっている28nm FD-SOIプロセス製品で変わる可能性はある」とするほか、「フレームワークについても、Caffe 2については2019年にサポートする予定だが、日本で人気のChainerについては、今のところサポートの予定はない」としている。

同社は2018年10月26日~19日にかけて千葉県・幕張メッセで開催されるCPS/IoTの総合展「CEATEC JAPAN 2018」において、これらのAI技術を用いた各種のデモを実施する予定としており、画像認識系のデモのみならず、キーフレーズの検出デモといったものも展示する予定だとしている。