英Armは現地時間の9月26日、車載向けでも特にADASに向けたプロセッサ「Cortex-A76AE」を発表した。型番から判るように、ベースとなるプロセッサはCortex-A76であり、7nmプロセスに向けて最適化された形で提供されるとする。

Cortex-A76は今年6月に発表されたばかりのモバイル向けのハイエンドプロセッサであるが、Cortex-A76AEはこれを16コア集積した状況で、30W以下の消費電力で250K DMIPS(250 DGIPSというべきか)の処理性能を実現できるとしている(Photo01)。

-

Photo01:SoC全体で30W未満、うちProcessor Coreが全部で15W未満ということで、コアあたり1W未満に抑えて利用という想定だと思われるが、むしろそれ以外に15Wも使うのか、という気もする

おそらく競合としては(現在はIntel傘下の)イスラエルMovileyeが2020年に提供予定とされるEyeQ5あたりになろうかと思われるが、こちらは5~6W以下のTDPで15T Ops/secの処理性能とされている。両者の性能の基準が違うので同列には比較できないが、ターゲットはレベル4以上の自動運転と考えられる。

モバイル向けのCortex-A76との主な違いは機能安全に関する部分である。ISO26262 ASIL-Dをサポートするために

- DCLS(Dual Core Lock-Step):2コアで対になる形でLock Step動作を行うことでASIL-Dで求められる10FIT未満の故障率を実現

- Memory Protection:L1はSECDED(Single Error Correction, Double Error Detection) ECC保護とパリティを付加、L2/L3にはSECDEC ECC保護を付加

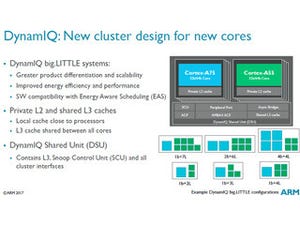

- RAS機能:Arm v8.2に準拠するRAS機能を内蔵しており、これにはコアおよびDSU(DynamIQ Shared Unit)のエラーレポーティング機能、テストのためのエラー注入/データ汚染機構などを含む

- コンパレータの内蔵:Lock-Step動作の際に2つのコアの動作を比較するためのコンパレータを内蔵

といった機能強化が図られている。

ちなみに当然このコアはDynamIQ環境で動作するわけだが、2つのコアが対になって1つのコアとして動作する関係で、OSからは8つのコアとして見える形になる様だ。

これらの機能とあわせて同時に発表されたのが、あたらしいSplit-Lockという機能である。これに関して説明しているArmのBlogエントリでも肝心な部分はボカされているのだが、このSplit-LockはLock-Stepをベースとしつつ、「起動時にSplit ModeとLock Modeを選ぶ事が可能で、Lock Modeを選ぶと通常のLock Step動作を、Split Modeを選ぶと2つのCPUがそれぞれ別のTaskを処理することが出来る」と説明されている。

ただ、2つのコアが独立モードとLock-Stepモードを選べるというだけであれば、例えば2015年にNXPが発表したMPC564xLでもLockstep ModeとDecoupled Modeが存在するなど、別に珍しくない。

ただこれと同じ動作をする場合、Lock Modeならば8コアとして動作するが、Split Modeでは16コアとして動くことになる。ところがDynamIQでは1つのProcessor Complex内に最大8コアまでしか統合できないから、コアが半分使えない事になってしまう(もしくは、最初から2つのDynamIQのComplexに分けて実装する形になるか、である)。ここから察するに、Split Modeを利用する場合、2つのCortex-A76AEコアの動作が、外から見るとあたかも1コアで動作している様に見せかけるようなトリックが実装されているのかもしれない。

実際前述のBlogエントリでも、「この(Split Modeを選べる)柔軟性は、エラーが発生した場合にシステムをシャットダウンするのではなく、(パフォーマンス)劣化モードで処理を継続できるように拡張することも出来る。例えばLock-Stepモードで動作している時に片方のコアが障害を起こした場合、システムを(一旦)停止し、障害のあるコアをSplit(オフライン)して、劣化モードでの継続が可能になる。この『分割可能』機能は、あらゆる自律システムにとって重要である」と説明されているあたり、単に別々のコアで動作するというだけでは無さそうである。

このあたりの詳細は、10月16日からサンノゼ(今年から会場がSJCCに変更になる)で開催されるArm TechCon 2018でもう少し紹介されることになるのではないかと思われる。