マサチューセッツ工科大学(MIT)とスタンフォード大学の研究チームは、論理回路とメモリを積層した新構造の三次元チップを開発した。人工知能(AI)による大量のデータ処理などを高速で行うのに適したデバイスであるとしている。論理回路はカーボンナノチューブ(CNT)で構成し、メモリには不揮発性の抵抗変化型メモリ(RRAM)を使用した。研究論文は、科学誌「Nature」に掲載された。

従来のコンピュータのアーキテクチャでは、演算処理を行う論理回路とデータ保存のためのメモリは別々のデバイスで構成し、これらのデバイス間を配線接続して信号のやり取りを行っている。しかし、デバイスの微細化が限界に近づくにつれて、デバイス間での信号やり取りにともなう遅延がコンピュータの性能を律速するボトルネックになってくる。

この問題を解決する方法として、論理回路とメモリを1つに統合し、論理層とメモリ層が三次元的に積層されたデバイス構造が考えられるが、従来のシリコン半導体のプロセスではこのような構造の形成は困難だった。

三次元デバイスが困難だった主な理由は、シリコン半導体のプロセス温度が1000℃以上と高いためであると研究チームは説明する。たとえば、まず論理回路の層を形成し、その上にメモリ層を形成するようなプロセスを行うと、先に作った論理層が熱によるダメージを受けてしまう。

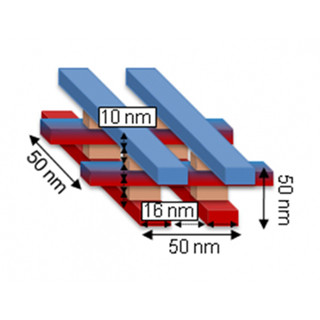

一方、今回報告されたデバイスでは、論理回路にCNT、メモリに絶縁体材料を用いて、プロセス温度を200℃未満に下げることができたため、論理層とメモリ層の積層構造の形成が可能になったと説明されている。

少し混乱しそうなので念のため補足しておくと、すでに実用化されている三次元積層メモリや三次元トランジスタにおける「三次元」という言い方は、メモリなどが形成された多数の極薄ウェハーを後工程で積層したもの、あるいは平面状のトランジスタを縦方向に並べた構造などを意味していることが多い。今回のように異種の機能をもった複数の層を前工程で三次元積層したデバイスとは区別する必要がある。

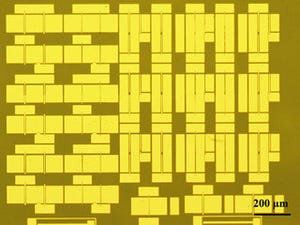

論文によると、今回試作されたデバイスは100mmシリコンウェハー上に集積形成されたもので、最下層にシリコンの論理回路が置かれ、その上にCNT電界トランジスタ(CNFET)による論理層、RRAM層(1Mビット)、さらにCNFET論理層が積層された4層構造となっている。最上層のCNFET論理層には大気ガスセンサとしての機能が備わっており、中間層のCNFET論理層には検知したガスの分類処理用アクセラレータなどの機能があるという。

カリフォルニア大学バークレー校電気工学・コンピュータサイエンス教授のJan Rabaey氏は、今回報告された三次元積層型アーキテクチャについて「脳型システムやディープニューラルネットのような機械学習ベースのコンピューティングに特に適しているのではないか」とコメントしている。

既存のシリコンベースのCMOS製造プロセスとの親和性も高いため、実用化しやすいことも強みであると研究チームは説明している。今後はマサチューセッツに拠点を置く半導体メーカーのアナログ・デバイセズと共同で新バージョンのチップ開発を進める予定であるという。