IBMは6月5日(米国時間)、研究協業のパートナーである米GLOBALFOUNDRIES(GF)、Samsung Electronicsおよび製造装置メーカーらとともに、5nmプロセスを実現するシリコンナノシート・トランジスタを採用したLSI製造向けシリコンウェハの製造に成功したと発表した。

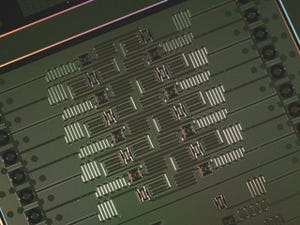

同プロセスの詳細は、6月5日~8日に京都で開催されている「VLSI Technplogy Symposium」で発表される予定(IBM Research Allianceによる論文「FinFETを超えたスケーリングを可能にするための積層ナノシート・ゲート・オールアラウンド・トランジスタ」)。IBMおよびパートナー企業の技術者たちは、200億個のトランジスタを搭載した7nmのテストノードを用いたチップを約2年前に開発していたが、今回は、さらに微細化をすすめ、指の爪の大きさに300億個のスイッチを搭載することに成功した。

5nmプロセスが実用化できれば、LSIの性能が今まで以上に向上するため、コグニティブコンピューティング、IoTおよびクラウドで提供されるその他のデータ集約型アプリケーションを加速させることにつながるとIBMでは説明。同プロセスを用いた場合、省電力化が進み、スマートフォンや他のモバイル製品のバッテリーが、既存の技術を適用した場合に比べて2~3倍長くなるという。

今回、研究グループは、米国ニューヨーク州の州都アルバニーにあるSUNY Polytechnic InstituteのCollege of nanoscale Science and Engineering(CNSE)キャンパスに設置されているIBMの300mm対応の研究開発ラインを用いて、FinFETの代わりに積層したシリコンナノシートをトランジスタのデバイス構造として用いることでブレークスルーを達成した。IBMが2014年に発表した5年間で30億ドルというチップ開発への投資により、実現できた成果であり、ナノシート・アーキテクチャにより、5nmノードへのスケーリングが実現できる可能性が示されたとする。

IBM Researchが進めてきたナノシート半導体技術の研究は、FinFETアーキテクチャよりも優れた電気的特性を備えた積層ナノシートデバイスを設計・製造できるかどうかを実証するものである。7nmの200億トランジスタの製造時にEUVリソグラフィを採用して以降、そのノウハウの集積を進めてきており、これにより今回、単一の製造プロセスおよびチップ設計でナノシートの幅を連続的に調節することができるようになったという。

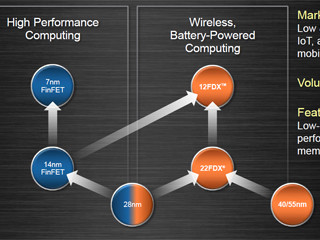

この調節は、物理的な幅を調整することで、特定の回路の性能と電力を同時に微調整するもの。FinFETトランジスタアーキテクチャは5nmまでは使用できるが、フィンの高さの制約でそうした微調整が不可能であり、フィン間のスペースを単純に縮小しても、性能向上のための電流増加ができないため、5nm以降の微細化には向かないとIBMは主張している。

ナノシートベースの5nmプロセス採用デバイスは、既存の先端プロセスとなる10nmプロセス採用デバイスと比較して、同一電力で40%の性能向上、または同一性能では75%の電力削減を実現できるとしている。

なお、IBMでは、「IBMは、業界の限界を打破するようなまったく新しいアーキテクチャや素材を積極的に追求し続け、そうした技術を詰め込んだ高性能メインフレームやコグニティブ・システムを市場に投入していく」とコメントしている。また、IBMの研究パートナーであり、IBMの半導体チームを吸収した経緯を有するGFでは、「IBMと同じニューヨーク州にあるGFのFab 8では、2018年より次世代プロセスである7nmの量産を計画しており、これにより半導体業界におけるテクノロジーリーダーシップを維持し、半導体製品の高性能化を推進していく」と述べている。