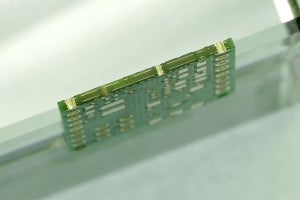

ザイリンクス(Xilinx)は5月17日、56G PAM4トランシーバーテクノロジーを、すでに量産出荷の実績がある16nm Virtex UltraScale+ FPGAと統合した製品として提供することを発表した。

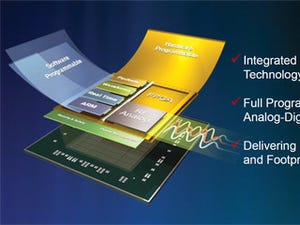

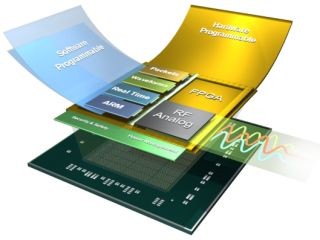

Virtex UltraScale+ FPGA に 56G PAM4トランシーバーテクノロジを統合したこれらのデバイスは、有線通信やデータセンター、無線バックホールアプリケーションを対象となっている。これらのデバイスの使うことで、56G+ラインレートでのデータ転送の物理的な限界を突破し、既存インフラの帯域幅を2倍にすることが可能だということだ。

同社は、すでに量産出荷の実績がある16nm FinFET+ FPGAファブリックを基盤として構成されたこれらのデバイスに関して、Virtex製品ラインを拡張して次なるイーサネット展開を推進するとともに、次世代のバックプレーン、光ファイバー通信、高性能インターコネクトへ既存システムを円滑に移行させるものだとしている。

なお、同社のSerDesテクノロジ グループ担当バイス プレジデントであるケン チャン(Ken Chang)氏は、「ザイリンクスは、56G PAM4を16nm FPGA へ統合することにより、これからもトランシーバー テクノロジをリードします。これらの新しいデバイスは実績のある FPGA を基盤として構成されており、間もなく展開される光ファイバー通信や、バックプレーンにおける広範なエコシステムとも調和が取れています」と述べている。